PC/104标准嵌入式扩展通信板设计

时间:06-30

来源:互联网

点击:

|

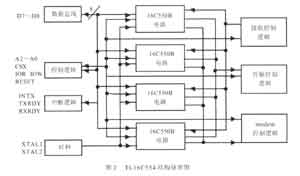

每一个内部的异步收发单元都等同于一个 16550,它向下兼容16450,包含了16字节的先进先出寄存器,从而减少了对CPU的中断次数。可编程设定的波特率最大可达1Mbps,接口的字符结构可由用户选择,自动完成起始位、停止位、奇偶校验位的加入和删除,具有可程序化中断控制和完整的MODEM控制逻辑功能。

2.3 PLD电路

考虑到104标准的尺寸限制,设计中应尽量采用紧凑的结构,因此用PLD电路来产生异步通信单元、数据缓冲电路的控制信号,还利用此电路实现 485连接时信号极性的自动转换。PLD电路采用了ALTERA公司的EPM7064,它包含了4个逻辑阵列块,64个宏单元,有1250个逻辑门可供使用。开发工具使用MAX+PLUSⅡ。

PLD电路主要完成以下功能:

(1)每一个异步收发单元的选择。利用八根地址信号A9~A3和读写控制信号IOR、IOW之间的逻辑关系产生片选信号,其中A9~A6 位地址信号同地址选择电路的信号一起先送到一个4位比较器中进行地址比较,地址选择电路可由用户设定,这样,通过改变地址选择电路中的短路块就改变了相应位的地址,从而增加了用户对地址的选择范围和使用的灵活性。

(2)双向数据缓冲器的片选。利用A 9~A6和读写控制信号产生。

(3)485信号极性选择。485采用总线方式连接,利用差分方式传输,两根连接线之间的信号正负极性不同,使用时必须使同极性端相连。

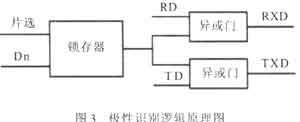

当节点之间比较远或者使用者并不清楚信号线的极性关系时往往不能保证正确接线,需要多次改变接线和调试,因此我们设计了极性的自动转换电路以方便嵌入式系统使用。基本思路是这样的,设置一个电子开关,在通信初始化期间由主机发一个固定的测试信号,如果从机发现接收到的信号不对,就自动切换电子开关换向,如果接收到的测试信号正确就保持原来的连接。电子开关由异或门充当,它可以反转或保持发送和接收的信号,即当输入端中的一个信号置1时就可使另一个输入信号在输出端反相,而当将其置0时输出信号保持不变。电子开关的控制由D触发器实现,在初始化期间从机根据所接收信号的正误,选通D触发器,产生合适的控制电平,实现电子开关的控制。其逻辑原理如图3所示。

|

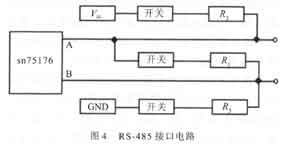

2.4 RS-485接口电路

当计算机利用RS-485总线方式通信,在进行系统连接时,需要在拓扑结构最远端的两个计算机的RS-485接口上加匹配电阻以消除信号的反射,还需要给信号传输线加一个固定的偏置电压以增加抗干扰能力。为了提高电路的通用性,方便嵌入式系统的使用,RS-485接口电路设计如图4。图中R 1=120Ω,R2=R3 =560Ω,在进行总线连接时就可以根据需要设置不同节点的计算机的RS-485 接口电路。

|

嵌入式 总线 电路 LTE 比较器 电子 电阻 电压 相关文章:

- 蓝牙无线电调制解调器Siw1701原理与应用(02-19)

- 嵌入式移动数据库的关键技术(03-20)

- 在嵌入式SQL中怎样使用游标(08-12)

- 嵌入式Linux系统软件开发学习思路详细介绍 (08-20)

- 基于AVR单片机的嵌入式“瘦服务器”系统设计思想(03-11)

- 嵌入式系统设计中的存储碎片收集策略(05-04)