基于AD6620和TMS320c6x的软件无线电接收子系统

时间:06-23

来源:互联网

点击:

软件无线电以其极强的灵活性和开放性代表着无线通信系统的发展趋势。其思想是以一个通用、标准、模块化的硬件平台为依托,通过软件编程实现无线通信系统的各种功能。

软件无线电提倡功能软件化,要求减少模拟环节。对接收机而言,则要求模/数转换器尽可能靠近天线。在现阶段,由于各种关键器件发展水平的限制,高频信号的直接数字化及其数据处理在成本上还不合算,因此数字中频软件无线电加上少量的高频模拟前端正成为理想软件无线电的一种经济、适用的选择。本数字中频接收子系统是基于数字下变频器DDCAD6620和数字信号处理器DSPTMS320C6701构建的。

1总体设计

1.1系统组成与信号处理流程

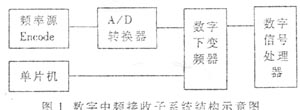

系统基本结构如图1所示。单片机实现数字下变频器的引导和初始化;高速ADC根据频率源Encode输入的时钟信号对输入信号进行过采样,并通过并行数据线向数字下变频器输出采样结果;数字下变频器根据单片机输入的数据设定数控振荡器NCO频率值、抽样率以及数字滤波器系数,据此对采样数据进行下变频、降低数据率和低通滤波处理,并通过串口将数据提供给DSP进行处理。

下面以一个实例说明信号处理流程。假设输入的中频信号的中心频率为456kHz,带宽为20kHz,fL、fH分别表示频率下限和上限,fL为446kHz,fH为466kHz。

如果如用Nyquist带通采样定理采样并设采样频率为fs,则要求:

fs=2(fi+fH)/(2n+1)

其中,n的取值应满足fs≥2(fH-fL)时的n的最大值。

取n为20,则带通取样频率为40.53kHz。如图2所示,(a)表示原始信号频谱,(b)表示以40.53kHz的采样频率采样后的信号频谱。对于处理信号而言,由于实际的20kHz带外还存在递减的干扰信号,倘若以40.53kHz采样率进行采样,就会出现较强的频谱混叠。

若用ADC对信号进行20MHz过采样?则如图2(c)所示,相邻信号频谱之间的间隔大大加宽,可充分避免频谱混叠。

本系统采用高速A/D转换芯片进行20MHz高速采样,输出的数据率为20MVPS。在目前的技术条件下,倘若过高的数据率直接输出给DSP,会占用DSP很多不必要的开销,所以需加入数字下变频器,在DSP前端将数据率降低。数字下变频器的主要功能有3个:(1)变频,将感兴趣的信号的中心频率变至零中频;(2)滤波,滤除带外干扰信号;(3)数率转换,通过降低数率,提供利于后续电路处理的低速数据。

1.2硬件电路设计

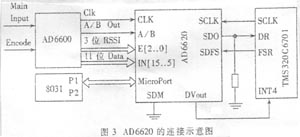

系统的硬件电路设计如图3所示。

数/模转换器采用的是AD公司生产的AD6600[1],它具有同时处理两路信号的能力。系统中Main Input向数/模转换器AD6600输入中频模拟信号,Encode给AD6600提供20MSPS的采样时钟。AD6600采样后的结果通过并行数据线输出给数字下变频器,并行数据线包括11位数据线和3位RSSI信号线(指数位)。

数字下变频器选用AD公司生产的AD6620[2]。如图3所示,AD6620的时钟信号是通过CLK由AD6600提供的。AD6600和AD6620都有两个数据通路A和B,具有同时处理两路信号的能力,它们通过A/B选择线协调相互间的工作模式。当AD6600只有一路信号需处理时,A/B选择线还可以用作输出数据的同步信号线。本例中仅有一路信号需要处理,所以只占用AD6600和AD6620的一个信号处理通路。由于AD6620的时钟信号CLK由AD6600直接提供,CLK同时起到了同步的作用,因此无需A/B用作同步信号线。在本系统中,本可将A/B拉高(当AD6600选择A通路时)或接地(当AD6600的选择B通路时)。但考虑到系统的通用性,还是将AD6600A/B和AD6620的A/B相连。AD6620的输入时序如图4所示。

在本例中,由单片机8031通过P1、P2口对AD6620的并行设置端口microport进行设置。AD6620通过串口SDO向DSP输出处理后的数据。由图3可见,AD6620的SDM接地,此时同步信号SCLK是由DSP传给AD6620的。在这种情况下,用Dvout来提示当前信号有效。SDFS表示数据帧的开始,在从模式下,该信号从DSP输入,AD6620在每个时钟周期的下降沿检测它。AD6620的输出时序如图5所示。首先,AD6620的Dvout引脚给DSP一个2~4个时钟周期的高电平信号通知DSP当前数据有效?然后DSP发回一个确认信号SDFS,表示一帧信号的开始。AD6620检测到SDFS为高电平后,在下一个时钟周期的上升沿开始输出信号。

DSP采用TI公司的TMS320C6701[3]。TMS320C6701包含8个并行的处理单元,采用甚长指令字(VLIW)结构,芯片最高时钟频率可达300MHz,最大处理能力可达2400MIPS。在本系统中,TMS320C6701的中断源INT4检测到中断信号以后,就会做好接收数据的准备,由FSR发出数据帧的帧同步信号,并由SCLK给出同步时钟,从DR输入信号。TMS320C6701对输入数据进行处理的程序的前几条指令放在中断源INT4在中断服务表中的中断服务取指包中。如果中断服务太长而不能放到一个取指包内,则加上一条跳转指令跳转到别的位置。

软件无线电提倡功能软件化,要求减少模拟环节。对接收机而言,则要求模/数转换器尽可能靠近天线。在现阶段,由于各种关键器件发展水平的限制,高频信号的直接数字化及其数据处理在成本上还不合算,因此数字中频软件无线电加上少量的高频模拟前端正成为理想软件无线电的一种经济、适用的选择。本数字中频接收子系统是基于数字下变频器DDCAD6620和数字信号处理器DSPTMS320C6701构建的。

1总体设计

1.1系统组成与信号处理流程

系统基本结构如图1所示。单片机实现数字下变频器的引导和初始化;高速ADC根据频率源Encode输入的时钟信号对输入信号进行过采样,并通过并行数据线向数字下变频器输出采样结果;数字下变频器根据单片机输入的数据设定数控振荡器NCO频率值、抽样率以及数字滤波器系数,据此对采样数据进行下变频、降低数据率和低通滤波处理,并通过串口将数据提供给DSP进行处理。

下面以一个实例说明信号处理流程。假设输入的中频信号的中心频率为456kHz,带宽为20kHz,fL、fH分别表示频率下限和上限,fL为446kHz,fH为466kHz。

如果如用Nyquist带通采样定理采样并设采样频率为fs,则要求:

fs=2(fi+fH)/(2n+1)

其中,n的取值应满足fs≥2(fH-fL)时的n的最大值。

取n为20,则带通取样频率为40.53kHz。如图2所示,(a)表示原始信号频谱,(b)表示以40.53kHz的采样频率采样后的信号频谱。对于处理信号而言,由于实际的20kHz带外还存在递减的干扰信号,倘若以40.53kHz采样率进行采样,就会出现较强的频谱混叠。

若用ADC对信号进行20MHz过采样?则如图2(c)所示,相邻信号频谱之间的间隔大大加宽,可充分避免频谱混叠。

本系统采用高速A/D转换芯片进行20MHz高速采样,输出的数据率为20MVPS。在目前的技术条件下,倘若过高的数据率直接输出给DSP,会占用DSP很多不必要的开销,所以需加入数字下变频器,在DSP前端将数据率降低。数字下变频器的主要功能有3个:(1)变频,将感兴趣的信号的中心频率变至零中频;(2)滤波,滤除带外干扰信号;(3)数率转换,通过降低数率,提供利于后续电路处理的低速数据。

1.2硬件电路设计

系统的硬件电路设计如图3所示。

数/模转换器采用的是AD公司生产的AD6600[1],它具有同时处理两路信号的能力。系统中Main Input向数/模转换器AD6600输入中频模拟信号,Encode给AD6600提供20MSPS的采样时钟。AD6600采样后的结果通过并行数据线输出给数字下变频器,并行数据线包括11位数据线和3位RSSI信号线(指数位)。

数字下变频器选用AD公司生产的AD6620[2]。如图3所示,AD6620的时钟信号是通过CLK由AD6600提供的。AD6600和AD6620都有两个数据通路A和B,具有同时处理两路信号的能力,它们通过A/B选择线协调相互间的工作模式。当AD6600只有一路信号需处理时,A/B选择线还可以用作输出数据的同步信号线。本例中仅有一路信号需要处理,所以只占用AD6600和AD6620的一个信号处理通路。由于AD6620的时钟信号CLK由AD6600直接提供,CLK同时起到了同步的作用,因此无需A/B用作同步信号线。在本系统中,本可将A/B拉高(当AD6600选择A通路时)或接地(当AD6600的选择B通路时)。但考虑到系统的通用性,还是将AD6600A/B和AD6620的A/B相连。AD6620的输入时序如图4所示。

在本例中,由单片机8031通过P1、P2口对AD6620的并行设置端口microport进行设置。AD6620通过串口SDO向DSP输出处理后的数据。由图3可见,AD6620的SDM接地,此时同步信号SCLK是由DSP传给AD6620的。在这种情况下,用Dvout来提示当前信号有效。SDFS表示数据帧的开始,在从模式下,该信号从DSP输入,AD6620在每个时钟周期的下降沿检测它。AD6620的输出时序如图5所示。首先,AD6620的Dvout引脚给DSP一个2~4个时钟周期的高电平信号通知DSP当前数据有效?然后DSP发回一个确认信号SDFS,表示一帧信号的开始。AD6620检测到SDFS为高电平后,在下一个时钟周期的上升沿开始输出信号。

DSP采用TI公司的TMS320C6701[3]。TMS320C6701包含8个并行的处理单元,采用甚长指令字(VLIW)结构,芯片最高时钟频率可达300MHz,最大处理能力可达2400MIPS。在本系统中,TMS320C6701的中断源INT4检测到中断信号以后,就会做好接收数据的准备,由FSR发出数据帧的帧同步信号,并由SCLK给出同步时钟,从DR输入信号。TMS320C6701对输入数据进行处理的程序的前几条指令放在中断源INT4在中断服务表中的中断服务取指包中。如果中断服务太长而不能放到一个取指包内,则加上一条跳转指令跳转到别的位置。

无线电 模拟前端 DSP 单片机 ADC 振荡器 滤波器 电路 MIPS 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)