UWB模块Wisair DV9110M配置的FPGA实现

时间:04-06

来源:互联网

点击:

引言

超宽带(UWB)技术近年来发展迅速,它创新的使用模式为拥挤的无线电频带来了新的应用理念。与传统无线技术相比,UWB技术具有频谱宽、功耗低、安全性高、不易产生干扰等优点,具有良好的市场前景。目前市场上主要的UWB厂商主要有Wisair公司、Wiquest公司等,其中Wisair公司推出的系列产品以其良好的可控性受到消费厂商的青眯。

DV9110M是Wisair推出的第二代基于Wimedia/MBOA标准的开发板,它体积小、集成度高,是一款多频带的OFDM收发器。它拥有两层结构,包括UWB子板和母板,其中UWB子板是核心,物理层和MAC层都位于子板之上,所有的外围接口则位于母板上。通过配置管理,DV9110M可以实现 6种不同的数据接口(最高数据传输率达200 Mbps),最高480 Mbps的物理层速度以及发送模块和接收模块的配对。

1 软件配置方式

Wisair提供了一种基于Windows的图形界面软件——Wisman,利用它主机可以通过USB接口读取或修改UWB设备的参数,如RF频率、包长、数据接口类型、物理层速率等,从而实现设备的配置和管理;同时还可监视发送和接收包的数目以及空中丢包率等,实时掌握UWB模块的工作情况。

2 配置的FPGA实现

2.1 问题的提出

Wisman操作简单,但由于DV9110M与主机通信的USB接口位于母板之上,因此使用Wisman时,必须采用两层结构。这样用户使用时再加上一层用户板,则至少需要三层结构,所占空间体积大,不利于系统集成。同时UWB母板使用5 V电源,使用时必须单独对其供电,增加了系统消耗。这些都成为限制其推广应用的瓶颈。

事实上,对UWB模块进行配置,最终都是通过对位于UWB子板上的芯片进行寄存器操作来实现的。对UWB子板而言,只需提供3.3 V工作电压以及正确的寄存器配置时序,就可正常实现UWB模块的数据收发功能,而这些依靠FPGA就可完成。这样用户使用时,只需一层FPGA板和一层 UWB子板,大大改善了系统结构。

2.2 FPGA实现

由于FPGA的工作电压足3.3 V,因此,为UWB子板提供3.3 V电压很容易。使用FPGA实现配置的关键在于对时序的控制。对UWB子板进行寄存器的相关操作是通过异步并行通信来完成的。该接口主要包括8位数据线,8位地址线和读写控制信号。整个寄存器地址空间呈线性分布,并被划分为若干页,每一页的最后一个地址FF用来控制页跳转。

配置寄存器的操作步骤如图1所示。第一步,设定被访问寄存器的页地址,此时,地址总线赋予“FF”,数据总线赋予页地址。第二步,对寄存器写入参数值,此时地址总线设定为该寄存器的页内地址,数据总线设为该寄存器要配置的值。

由于是异步通信,因此必须保证最小的时序间隔:其中低有效的写控制信号的持续时间必须大于76 ns,而相邻两次写操作时间间隔必须大于60 ns。同时,为了配置成功,还应保证在写控制信号有效时,数据和地址信号保持稳定,具体流程如图2所示。

包含配置地址和数据信息的文档位于Wisman安装目录下的Default_NoAck.txt中。默认需要顺序配置4 195个寄存器。此外,对于特定接口(如以太网接口)以及特定参数(如物理层速率,调频序列等)需要另行配置,共有8个相关寄存器。因此总共需要配置的寄存器为4 203个。由于配置一个寄存器需要获知16位地址信息和8位数据信息,因此一个寄存器需要存储的信息量为24位,而需要配置的寄存器达4 203个,如果将这些信息全固化入ROM中,将占用大量的FPGA资源,不利于系统其他功能的开发。为此,针对这4 203个寄存器,进行分类优化,一共可分为三个部分:

第一部分是前5个寄存器。这5个寄存器的地址和数据没有规律,但由于数量很少,配置时枚举即可。

第二部分包括41组寄存器,共4 052个。其中每组寄存器的起始地址都相同,偏移地址在起始地址的基础上依次增加1。配置这部分寄存器时,只需用ROM存储8位的数据信息,其地址信息则由该组寄存器的起始地址以及该寄存器的配置顺序号决定。这样24位宽的ROM变为8位宽,大大减少了资源。

第三部分包括148个寄存器,其地址和数据也没有规律,对这部分寄存器信息用24位的ROM来存储。

3 仿真结果与资源使用量

通过使用FPGA来代替软件完成配置,一层子板就可实现UWB模块的数据收发功能,其高度由20 mm变为10 mm,降低了50%,大大压缩了体积,有利于UWB模块在使用时的设备集成;去掉了母板,用FPGA来提供UWB子板的电压,节省了一个需单独供电的5 V电源,而且节省了器件,降低了功耗;同时由于减少了母板的中转,接口时钟从25 MHz提高到30MHz,理论带宽由200 MHz提高到240 MHz,提高了20%,在数据的无线传输过程中具有重大的意义。

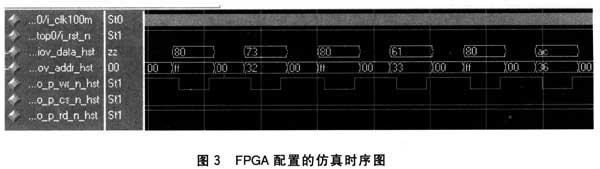

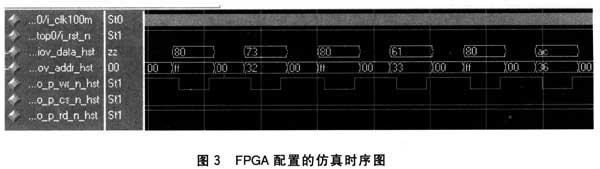

最终仿真波形如图3所示。

如果用Xilinx Virtex4系列的xc4lxl5器件来综合,最后使用的资源如表1所列。

超宽带(UWB)技术近年来发展迅速,它创新的使用模式为拥挤的无线电频带来了新的应用理念。与传统无线技术相比,UWB技术具有频谱宽、功耗低、安全性高、不易产生干扰等优点,具有良好的市场前景。目前市场上主要的UWB厂商主要有Wisair公司、Wiquest公司等,其中Wisair公司推出的系列产品以其良好的可控性受到消费厂商的青眯。

DV9110M是Wisair推出的第二代基于Wimedia/MBOA标准的开发板,它体积小、集成度高,是一款多频带的OFDM收发器。它拥有两层结构,包括UWB子板和母板,其中UWB子板是核心,物理层和MAC层都位于子板之上,所有的外围接口则位于母板上。通过配置管理,DV9110M可以实现 6种不同的数据接口(最高数据传输率达200 Mbps),最高480 Mbps的物理层速度以及发送模块和接收模块的配对。

1 软件配置方式

Wisair提供了一种基于Windows的图形界面软件——Wisman,利用它主机可以通过USB接口读取或修改UWB设备的参数,如RF频率、包长、数据接口类型、物理层速率等,从而实现设备的配置和管理;同时还可监视发送和接收包的数目以及空中丢包率等,实时掌握UWB模块的工作情况。

2 配置的FPGA实现

2.1 问题的提出

Wisman操作简单,但由于DV9110M与主机通信的USB接口位于母板之上,因此使用Wisman时,必须采用两层结构。这样用户使用时再加上一层用户板,则至少需要三层结构,所占空间体积大,不利于系统集成。同时UWB母板使用5 V电源,使用时必须单独对其供电,增加了系统消耗。这些都成为限制其推广应用的瓶颈。

事实上,对UWB模块进行配置,最终都是通过对位于UWB子板上的芯片进行寄存器操作来实现的。对UWB子板而言,只需提供3.3 V工作电压以及正确的寄存器配置时序,就可正常实现UWB模块的数据收发功能,而这些依靠FPGA就可完成。这样用户使用时,只需一层FPGA板和一层 UWB子板,大大改善了系统结构。

2.2 FPGA实现

由于FPGA的工作电压足3.3 V,因此,为UWB子板提供3.3 V电压很容易。使用FPGA实现配置的关键在于对时序的控制。对UWB子板进行寄存器的相关操作是通过异步并行通信来完成的。该接口主要包括8位数据线,8位地址线和读写控制信号。整个寄存器地址空间呈线性分布,并被划分为若干页,每一页的最后一个地址FF用来控制页跳转。

配置寄存器的操作步骤如图1所示。第一步,设定被访问寄存器的页地址,此时,地址总线赋予“FF”,数据总线赋予页地址。第二步,对寄存器写入参数值,此时地址总线设定为该寄存器的页内地址,数据总线设为该寄存器要配置的值。

由于是异步通信,因此必须保证最小的时序间隔:其中低有效的写控制信号的持续时间必须大于76 ns,而相邻两次写操作时间间隔必须大于60 ns。同时,为了配置成功,还应保证在写控制信号有效时,数据和地址信号保持稳定,具体流程如图2所示。

包含配置地址和数据信息的文档位于Wisman安装目录下的Default_NoAck.txt中。默认需要顺序配置4 195个寄存器。此外,对于特定接口(如以太网接口)以及特定参数(如物理层速率,调频序列等)需要另行配置,共有8个相关寄存器。因此总共需要配置的寄存器为4 203个。由于配置一个寄存器需要获知16位地址信息和8位数据信息,因此一个寄存器需要存储的信息量为24位,而需要配置的寄存器达4 203个,如果将这些信息全固化入ROM中,将占用大量的FPGA资源,不利于系统其他功能的开发。为此,针对这4 203个寄存器,进行分类优化,一共可分为三个部分:

第一部分是前5个寄存器。这5个寄存器的地址和数据没有规律,但由于数量很少,配置时枚举即可。

第二部分包括41组寄存器,共4 052个。其中每组寄存器的起始地址都相同,偏移地址在起始地址的基础上依次增加1。配置这部分寄存器时,只需用ROM存储8位的数据信息,其地址信息则由该组寄存器的起始地址以及该寄存器的配置顺序号决定。这样24位宽的ROM变为8位宽,大大减少了资源。

第三部分包括148个寄存器,其地址和数据也没有规律,对这部分寄存器信息用24位的ROM来存储。

3 仿真结果与资源使用量

通过使用FPGA来代替软件完成配置,一层子板就可实现UWB模块的数据收发功能,其高度由20 mm变为10 mm,降低了50%,大大压缩了体积,有利于UWB模块在使用时的设备集成;去掉了母板,用FPGA来提供UWB子板的电压,节省了一个需单独供电的5 V电源,而且节省了器件,降低了功耗;同时由于减少了母板的中转,接口时钟从25 MHz提高到30MHz,理论带宽由200 MHz提高到240 MHz,提高了20%,在数据的无线传输过程中具有重大的意义。

最终仿真波形如图3所示。

如果用Xilinx Virtex4系列的xc4lxl5器件来综合,最后使用的资源如表1所列。

无线电 收发器 USB FPGA 电压 总线 仿真 Xilinx 电子 Verilog 单片机 嵌入式 相关文章:

- 软件无线电的电磁兼容分析(02-26)

- 对信息技术设备的无线电骚扰管理方法的研究(02-27)

- 雷达信号及其监测研究(03-02)

- 基于认知无线电技术的IEEE 802.22(10-02)

- 4G移动通信关键技术及特征(03-09)

- 无线电频率资源的合理配置(08-16)