嵌入式系统的PCIe时钟分配

时间:12-09

来源:互联网

点击:

PCIe抖动的测量

在深入分析这个解决方案的性能之前,需要先讨论 PCIe抖动性能的分析过程。PCIe抖动工作组关注的一个首要问题是确定一个恰当的基准时钟。为实现这个目的,需要考虑基准时钟的Tx和Rx PLL及相位插值器的过滤效果。同时,为避免对基准时钟规格不足,这些PLL的峰值效应也需要考虑。这一过程分为四个主要步骤:

1.确定每个周期累积的相位误差。串行数据传输不像并行数据传输那样关心时钟的Cycle-to-Cycle抖动和Period抖动,串行数据传输更关心累积相位误。因此,我们必须首先确定每个时钟周期的累积相位误差。

2.将离散傅立叶变换(Discrete Fourier Transform,简称DFT)用于累积相位误差数据,从而将时域的分析转变到频域进行分析。

3.将系统转移函数用于累积相位误差数据的DFT。

4.执行逆DFT,使过滤后的累积相位误差数据转回到时域内,这便是最终结果。

同时还要注意,通过设定系统转移函数s=jω,可以在复杂的频域实现PLL系统的过滤分析。该分析对连续系统很有用,但由于采用相位检测器和反馈除法器等数字元件,大多数现代PLL方案不是纯粹的模拟系统,因而z域数字分析会更精确。但是,PCI抖动工作组的初步研究表明,受s域分析影响的误差最小,因此s 域分析可用于建模。然而,当基频低于PLL环路带宽10倍时,s域近似值会显著背离真值,所以系统设计师在选择PLL时必须时刻谨记这一点。

有关这一过程的更多信息和背景资料,请查阅IDT应用笔记《PCIe基准时钟要求》。

抖动测量技巧

测量方法不当很容易得到两倍以上于正确方法的抖动测量值。这里有一些技巧:

1.从被测器件到示波器都使用屏蔽同轴电缆,并在示波器的输入端做好恰当的匹配。

2.如果使用高阻抗探头,可使用低电容探头和接地夹,而非电线。

3.确保你使用了与样本量一致的最高采样率。

4.使示波器屏幕上的纵坐标最大,以便精确地测量电压。

5.使显示器、开关式电源和手机远离被测器件。可行时使用线性电源。

6.当执行差分测量时,确保两条电缆已经相互纠偏。

IDT解决方案分析

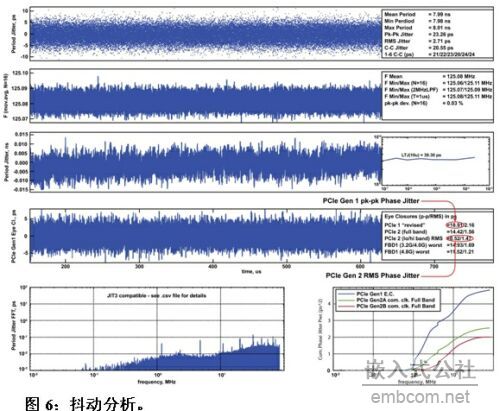

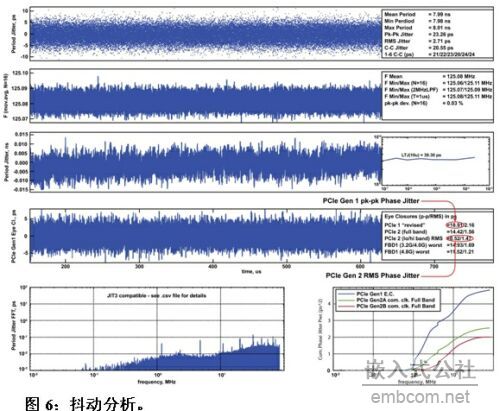

IDT 的工程师通过菊链三个特性描述板以代表子卡:ICS841S32I板,然后是ICS8743008I板,最后一个也是ICS8743008I板,创建了解决方案的原型,见图5。在第二个ICS8743008I输出时进行测量。卸载来自示波器的时钟周期数据,然后由抖动分析脚本进行后处理。该脚本可进行必要的频域和时域分析。

嵌入式系统的PCIe时钟分配

2.5Gbps 分析方法的结果为18.91ps。这一结果符合4.5倍的裕量的86ps的PCIe峰-峰相位抖动指标。对于5.0Gbps操作,PCIe规定了rms相位抖动,而非峰-峰相位抖动。这些结果也超出了规范:0.52psrms低频带和1.47ps高频带与3.1ps规范限制之比。

对于5.0Gbps工作,PCIe为频域分析规定了两个转移函数和两个频率范围。第一个转移函数的极频率为5MHz和16MHz,第二个转移函数的极频率为 8MHz和16MHz。抖动分析所得的两个频段为10KHz-1.5MHz(低频带),1.5MHz-Nyquist(高频带)。Nyquist表示分析达到了基准时钟频率的一半。例如,在100MHz时,频域分析将达到50MHz。分析脚本会显示每个频率分析频带间两个转移函数间的最差情况。

小结

PCIe标准最初用于定义PC系统,但由于其低引脚数和可扩展的高性能,很快成为几乎所有应用领域选择的I/O接口。高速的基准时钟给希望利用PCIe元件的嵌入式系统工程师们提出了严峻的挑战,他们需要分配、选择两个不同的符合规范的基准时钟速度。

这个测试解决方案有助于系统利用支持100MHz和125MHz基准时钟的元件,并通过一个M-LVDS差分对将其分配到系统的所有卡上。该解决方案也可以对卡进行设置,因此这些卡可以在其应用指令下作为主或端点操作,而且能插入系统的任何插槽。另外,这一解决方案降低了背板上基准时钟的工作频率,放宽了该信号的路由限制和串扰性能。只要满足2.5Gbps和5.0Gbps操作PCIe规范严格的抖动要求,所有这些都可以用一个设计实现。

作者:IDT公司Ian Dobson,Jim Holbrook

在深入分析这个解决方案的性能之前,需要先讨论 PCIe抖动性能的分析过程。PCIe抖动工作组关注的一个首要问题是确定一个恰当的基准时钟。为实现这个目的,需要考虑基准时钟的Tx和Rx PLL及相位插值器的过滤效果。同时,为避免对基准时钟规格不足,这些PLL的峰值效应也需要考虑。这一过程分为四个主要步骤:

1.确定每个周期累积的相位误差。串行数据传输不像并行数据传输那样关心时钟的Cycle-to-Cycle抖动和Period抖动,串行数据传输更关心累积相位误。因此,我们必须首先确定每个时钟周期的累积相位误差。

2.将离散傅立叶变换(Discrete Fourier Transform,简称DFT)用于累积相位误差数据,从而将时域的分析转变到频域进行分析。

3.将系统转移函数用于累积相位误差数据的DFT。

4.执行逆DFT,使过滤后的累积相位误差数据转回到时域内,这便是最终结果。

同时还要注意,通过设定系统转移函数s=jω,可以在复杂的频域实现PLL系统的过滤分析。该分析对连续系统很有用,但由于采用相位检测器和反馈除法器等数字元件,大多数现代PLL方案不是纯粹的模拟系统,因而z域数字分析会更精确。但是,PCI抖动工作组的初步研究表明,受s域分析影响的误差最小,因此s 域分析可用于建模。然而,当基频低于PLL环路带宽10倍时,s域近似值会显著背离真值,所以系统设计师在选择PLL时必须时刻谨记这一点。

有关这一过程的更多信息和背景资料,请查阅IDT应用笔记《PCIe基准时钟要求》。

抖动测量技巧

测量方法不当很容易得到两倍以上于正确方法的抖动测量值。这里有一些技巧:

1.从被测器件到示波器都使用屏蔽同轴电缆,并在示波器的输入端做好恰当的匹配。

2.如果使用高阻抗探头,可使用低电容探头和接地夹,而非电线。

3.确保你使用了与样本量一致的最高采样率。

4.使示波器屏幕上的纵坐标最大,以便精确地测量电压。

5.使显示器、开关式电源和手机远离被测器件。可行时使用线性电源。

6.当执行差分测量时,确保两条电缆已经相互纠偏。

IDT解决方案分析

IDT 的工程师通过菊链三个特性描述板以代表子卡:ICS841S32I板,然后是ICS8743008I板,最后一个也是ICS8743008I板,创建了解决方案的原型,见图5。在第二个ICS8743008I输出时进行测量。卸载来自示波器的时钟周期数据,然后由抖动分析脚本进行后处理。该脚本可进行必要的频域和时域分析。

嵌入式系统的PCIe时钟分配

2.5Gbps 分析方法的结果为18.91ps。这一结果符合4.5倍的裕量的86ps的PCIe峰-峰相位抖动指标。对于5.0Gbps操作,PCIe规定了rms相位抖动,而非峰-峰相位抖动。这些结果也超出了规范:0.52psrms低频带和1.47ps高频带与3.1ps规范限制之比。

对于5.0Gbps工作,PCIe为频域分析规定了两个转移函数和两个频率范围。第一个转移函数的极频率为5MHz和16MHz,第二个转移函数的极频率为 8MHz和16MHz。抖动分析所得的两个频段为10KHz-1.5MHz(低频带),1.5MHz-Nyquist(高频带)。Nyquist表示分析达到了基准时钟频率的一半。例如,在100MHz时,频域分析将达到50MHz。分析脚本会显示每个频率分析频带间两个转移函数间的最差情况。

小结

PCIe标准最初用于定义PC系统,但由于其低引脚数和可扩展的高性能,很快成为几乎所有应用领域选择的I/O接口。高速的基准时钟给希望利用PCIe元件的嵌入式系统工程师们提出了严峻的挑战,他们需要分配、选择两个不同的符合规范的基准时钟速度。

这个测试解决方案有助于系统利用支持100MHz和125MHz基准时钟的元件,并通过一个M-LVDS差分对将其分配到系统的所有卡上。该解决方案也可以对卡进行设置,因此这些卡可以在其应用指令下作为主或端点操作,而且能插入系统的任何插槽。另外,这一解决方案降低了背板上基准时钟的工作频率,放宽了该信号的路由限制和串扰性能。只要满足2.5Gbps和5.0Gbps操作PCIe规范严格的抖动要求,所有这些都可以用一个设计实现。

作者:IDT公司Ian Dobson,Jim Holbrook

嵌入式 连接器 收发器 电压 电路 IDT 示波器 电容 显示器 相关文章:

- 蓝牙无线电调制解调器Siw1701原理与应用(02-19)

- 嵌入式移动数据库的关键技术(03-20)

- 在嵌入式SQL中怎样使用游标(08-12)

- 嵌入式Linux系统软件开发学习思路详细介绍 (08-20)

- 基于AVR单片机的嵌入式“瘦服务器”系统设计思想(03-11)

- 嵌入式系统设计中的存储碎片收集策略(05-04)