串行RapidIO在WiMAX基站系统中的应用

时间:12-21

来源:互联网

点击:

无线基站系统设计

无线基站是典型的高性能嵌入式通信系统,它们对互连的带宽、时延、复杂度、灵活性、可靠性都有非常高的要求。而串行RapidIO正是满足这些要求的最佳选择。

无线基站系统

在传统的基站系统中,DSP与PowerPC或FPGA之间的互连一般用外部存储器接口EMIF;DSP之间或DSP与主机之间一般用 HPI(Host Port Interface)或PCI互连。它们的主要缺点是:带宽小、信号线多、主从模式接口,不支持对等传输。另外,DSP不能直接进行背板传输。如果利用串行 RapidIO 进行DSP互连则可以大大提高效率,一来它可将用于实现 DSP 之间高速互连的信号引脚数减到最少,二来可简化处理器之间的通信,从而有效地降低系统成本。

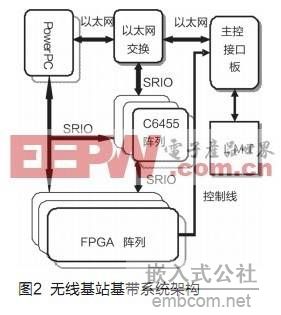

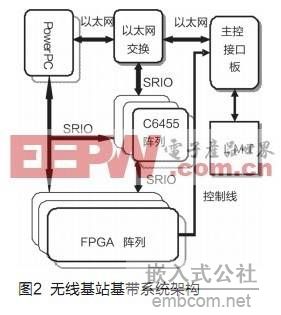

图2所示系统是基于CPU的高性能DSP系统。PowerPC主要针对无需大量乘法运算的一般应用,如MAC层处理。DSP主要完成滤波、矢量乘法和查找以及图像或视频分析等信号处理操作。FPGA实现FFT或者PAPR算法等。

图2所示的无线基站基带系统具有极高的灵活性和可扩展性,在这种架构中,各个处理器的任务分工具有很大的灵活性。由于架构已经不再与运算密切相关,流量和处理能力可在运行时间内从一个器件转移到另外一个器件。该架构也具有可扩展性,有助于满足具体应用在性能和成本方面所需的端点数量增减。例如,可以轻易改变 DSP型号和 DSP 数量,以实现相同的设计可以匹配到从微蜂窝到大型基站的设计要求。要在降低成本同时满足更高性能和带宽,关键在于采用模块化和基于标准的架构。构建下一代基带卡和基于连接了多个DSP、FPGA 和 ASIC 的串行RapidIO 接口的结构型架构具有许多优势。

系统在WiMAX BBU中的应用

·WiMAX BBU系统架构

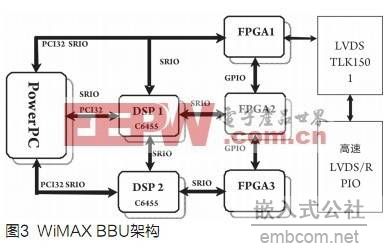

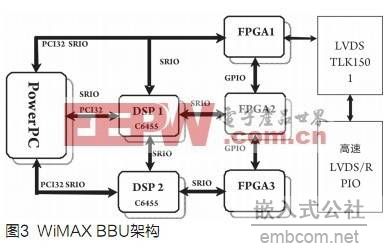

图3是基于图2的WiMAX BBU系统,该系统硬件上包括一片PPC处理器MPC8548,两片DSP处理器(TI的C6455)和三片Xilinx FPGA V5LX110。FPGA与DSP之间使用SRIO口通信,DSP与PPC之间使用PCI接口和SRIO进行通信,FPGA之间使用仿PCI接口进行通信。DSP1与DSP2之间使用SRIO接口进行通信。

本系统中还保留PowerPC与DSPC6455的 PCI32互连,这样有利于boot模式下程序的下载。FPGA1主要实现IFFT和PAPR算法;FPGA2主要实现RANGING和FFT算法;DSP1主要实现信道编码、调制、空时编码和子载波映射,DSP2主要实现信道解码、解调、信道估计和子载波解映射。FPGA3主要实现TURBO的解码。另外MIMO的上行算法会在DSP2、FPGA2和DSP1上协同处理。

·测试结果

在4x模式下,测试DSP1与DSP2之间的通信速率和出错率。

测试方案:DSP1为主机,DSP2为从机。主机向从机发送数据,I/O模式下,数据发送完毕主机发送doorbell告知从机,并读回 DSP2所接收的数据比较数据是否出错;message模式下,数据链发送完毕硬件会产生中断,进入中断服务程序,接收端接收完数据链也是自动产生中断,只需记录中断次数就能判断数据是否传送正常。

选择3.125G波特率进行1x模式通信。测试结果如表1。结果表明SRIO的高传送性能能满足WiMAX 基带处理要求并验证了本文提出的WiMAX BBU系统架构的可行性和可靠性。

结语

本文提出的无线基站基带系统架构具有高计算速率,高带宽,可行性和可扩展性等特点。此系统架构已实际应用到WiMAX BBU系统,还可用于多种无线信号处理模块,如雷达干扰系统等。在不同的嵌入式系统中各个处理器的任务分工会有所不同,SRIO技术的实现也具有很大的灵活性,比如:可以用Direct I/O逻辑模式或者message模式实现通信等。

参考文献:

[1] 汪安民, 张胜波.C645x的串行RapidIO总线通信系统设计[J]. 单片机与嵌入式系统应用, 2008(11)

[2]杨涛. RapidIO互联技术在下一代无线基站中的应用[D]. 西安: 西安电子科技大学, 2008

[3] 王勇. 基于Virtex-5 FPGA设计Gbps无线通信基站[J].电子产品世界,2008(11)

[4] Tim B, Fred S. High-PerformanceScalable Computing for Real-time Applications, Computer Communications and Networks, Proceedings of 6th International Conference[C], 1997:332-335

[5] TI. TMS320C645x Serial Rapid IO (SRIO)User’s Guide, 2006

作者:朱朝平 樊利民 华南理工大学电力学院 陈军 华南理工大学电子与信息学院 时间:2009-12-10

无线基站是典型的高性能嵌入式通信系统,它们对互连的带宽、时延、复杂度、灵活性、可靠性都有非常高的要求。而串行RapidIO正是满足这些要求的最佳选择。

无线基站系统

在传统的基站系统中,DSP与PowerPC或FPGA之间的互连一般用外部存储器接口EMIF;DSP之间或DSP与主机之间一般用 HPI(Host Port Interface)或PCI互连。它们的主要缺点是:带宽小、信号线多、主从模式接口,不支持对等传输。另外,DSP不能直接进行背板传输。如果利用串行 RapidIO 进行DSP互连则可以大大提高效率,一来它可将用于实现 DSP 之间高速互连的信号引脚数减到最少,二来可简化处理器之间的通信,从而有效地降低系统成本。

图2所示系统是基于CPU的高性能DSP系统。PowerPC主要针对无需大量乘法运算的一般应用,如MAC层处理。DSP主要完成滤波、矢量乘法和查找以及图像或视频分析等信号处理操作。FPGA实现FFT或者PAPR算法等。

图2所示的无线基站基带系统具有极高的灵活性和可扩展性,在这种架构中,各个处理器的任务分工具有很大的灵活性。由于架构已经不再与运算密切相关,流量和处理能力可在运行时间内从一个器件转移到另外一个器件。该架构也具有可扩展性,有助于满足具体应用在性能和成本方面所需的端点数量增减。例如,可以轻易改变 DSP型号和 DSP 数量,以实现相同的设计可以匹配到从微蜂窝到大型基站的设计要求。要在降低成本同时满足更高性能和带宽,关键在于采用模块化和基于标准的架构。构建下一代基带卡和基于连接了多个DSP、FPGA 和 ASIC 的串行RapidIO 接口的结构型架构具有许多优势。

系统在WiMAX BBU中的应用

·WiMAX BBU系统架构

图3是基于图2的WiMAX BBU系统,该系统硬件上包括一片PPC处理器MPC8548,两片DSP处理器(TI的C6455)和三片Xilinx FPGA V5LX110。FPGA与DSP之间使用SRIO口通信,DSP与PPC之间使用PCI接口和SRIO进行通信,FPGA之间使用仿PCI接口进行通信。DSP1与DSP2之间使用SRIO接口进行通信。

本系统中还保留PowerPC与DSPC6455的 PCI32互连,这样有利于boot模式下程序的下载。FPGA1主要实现IFFT和PAPR算法;FPGA2主要实现RANGING和FFT算法;DSP1主要实现信道编码、调制、空时编码和子载波映射,DSP2主要实现信道解码、解调、信道估计和子载波解映射。FPGA3主要实现TURBO的解码。另外MIMO的上行算法会在DSP2、FPGA2和DSP1上协同处理。

·测试结果

在4x模式下,测试DSP1与DSP2之间的通信速率和出错率。

测试方案:DSP1为主机,DSP2为从机。主机向从机发送数据,I/O模式下,数据发送完毕主机发送doorbell告知从机,并读回 DSP2所接收的数据比较数据是否出错;message模式下,数据链发送完毕硬件会产生中断,进入中断服务程序,接收端接收完数据链也是自动产生中断,只需记录中断次数就能判断数据是否传送正常。

选择3.125G波特率进行1x模式通信。测试结果如表1。结果表明SRIO的高传送性能能满足WiMAX 基带处理要求并验证了本文提出的WiMAX BBU系统架构的可行性和可靠性。

结语

本文提出的无线基站基带系统架构具有高计算速率,高带宽,可行性和可扩展性等特点。此系统架构已实际应用到WiMAX BBU系统,还可用于多种无线信号处理模块,如雷达干扰系统等。在不同的嵌入式系统中各个处理器的任务分工会有所不同,SRIO技术的实现也具有很大的灵活性,比如:可以用Direct I/O逻辑模式或者message模式实现通信等。

参考文献:

[1] 汪安民, 张胜波.C645x的串行RapidIO总线通信系统设计[J]. 单片机与嵌入式系统应用, 2008(11)

[2]杨涛. RapidIO互联技术在下一代无线基站中的应用[D]. 西安: 西安电子科技大学, 2008

[3] 王勇. 基于Virtex-5 FPGA设计Gbps无线通信基站[J].电子产品世界,2008(11)

[4] Tim B, Fred S. High-PerformanceScalable Computing for Real-time Applications, Computer Communications and Networks, Proceedings of 6th International Conference[C], 1997:332-335

[5] TI. TMS320C645x Serial Rapid IO (SRIO)User’s Guide, 2006

作者:朱朝平 樊利民 华南理工大学电力学院 陈军 华南理工大学电子与信息学院 时间:2009-12-10

LTE DSP FPGA 总线 嵌入式 Xilinx MIPS 单片机 电子 相关文章:

- 3G LTE简介(01-30)

- LTE——3G技术的未来发展(02-20)

- 3GPP LTE/SAE网络体系结构和标准化进展(04-14)

- TD向LTE TDD平滑演进(04-21)

- LTE技术热点分析(09-19)

- UMB、LTE、WiMAX谁是移动通信发展方向(09-30)