将可制造性设计(DFM)应用于PCB开发

时间:09-28

来源:互联网

点击:

作者:Nexlogic Technologies公司 Syed Wasif Ali

在可制造性设计(DFM)中,PCB设计布线工程师会很容易地忽略咋看起来不那么重要的关键因素。但在后继流程,这些因素在制造过程中发挥着重要作用,可能成为不佳良率的根本原因。

当涉及高速PCB设计,特别是高于20GHz时,若PCB设计和制造团队间缺乏沟通和/或彼此产生错误的预设和解读,就可在制造过程中导致代价高昂的失败。以下列举了一些沟通出问题时的真实情况,并就如何避免此类问题给出了一些建议。

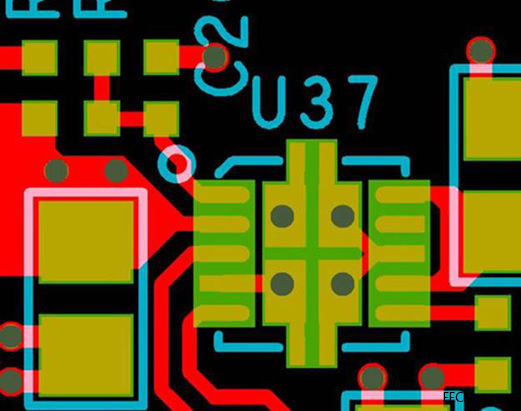

情景1:缩小焊盘尺寸以匹配线宽

在此例,PCB设计师缩小了焊盘尺寸以匹配线宽。他虽没有三思而行,但这种作法完全可以接受。不幸的是,他缩小的太多了,以致成为一个违反IPC(国际电子工业连接协会)约定和制造规则的灾难。

其结果是在制造过程中,出现一系列问题;特别是如图1所示的翘脱(又称墓碑效应,tombstoning)现象的发生。翘脱是发生在PCB焊装阶段的一种器件焊接缺陷,由回流过程中焊料的表面张力所引起。其现象是:器件的一端翘脱、凸起、支离于PCB的铜焊盘,类似一个突起的墓碑。

图1:翘脱

这是因为导线与焊盘粗细一样,所以焊料流入导线,且在回流期间焊料有移动。其结果就造成焊垫大小的不匹配。加上其它DFM问题,使良率低于60%,远低于预期的90%。

其它DFM问题有:

* 批开放阻焊(gang relief mask)工艺造成的焊料短路

* 使用热通孔造成焊料沿孔壁溢流

* 两个焊盘之间阻焊不充分

实际上,PCB设计者使线宽粗细等同焊盘大小的决定,着实无可厚非:在任何高速信号链路中,当信号路径的几何形状改变时,会发生阻抗不连续的情况,从而导致信号路径阻抗的改变。通过使用相同粗细的线径和焊盘,信号通路的几何形状不会改变,当导线接入分立元件的焊盘时,阻抗的不连续问题得以缓解。这在理论上是成立的。但在实践中,当导线太细、焊盘太小时,仍采用两者相同的策略,则会产生翘脱等其它类似的制造性问题。

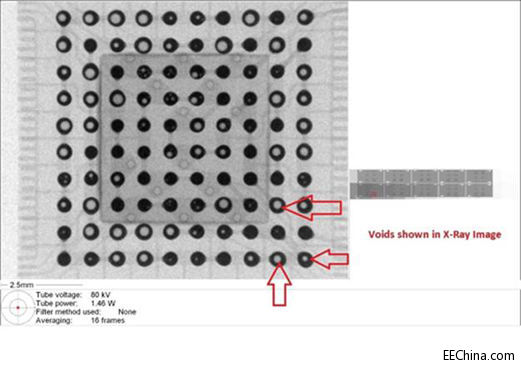

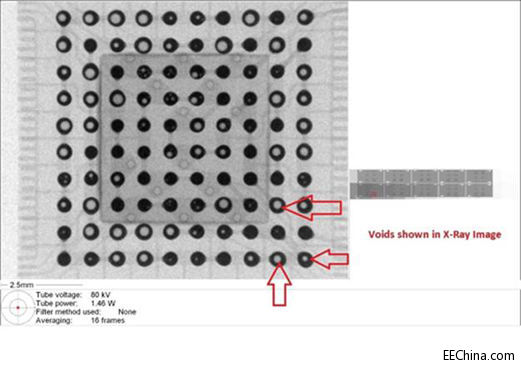

具体地,在本例,扇出导线与焊盘尺寸相同。此处,采用一个BGA封装,其BGA焊盘以较粗的导线扇出。如果它不是一个非阻焊定义(NSMD)的焊盘,则焊料就将流入从那些特定焊盘扇出的导线,并会在BGA器件的下方造成焊盘大小不一致,并随后形成冷焊点(虚焊)或空隙,如图所示2。

图2:BGA内的空隙

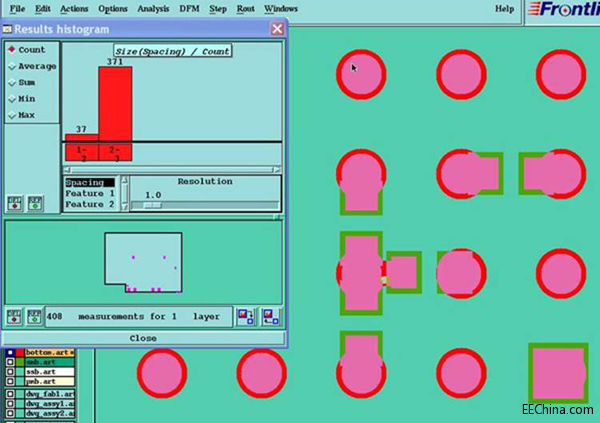

情景2:射频滤波器问题

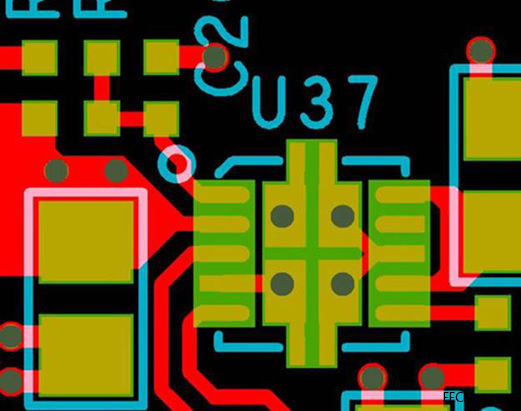

本例,高速设计包含一个专用、三引脚SOP封装的射频滤波器。在SOP的引脚间没使用阻焊层,对这些引脚采用的是批开放处理,批开放阻焊(gang relieve mask)工艺是定义阻焊层的一种方法,它约定不对一组管脚进行阻焊。其结果是一组管脚间彼此没有阻焊隔离。这可以是刻意达成的效果,也可能是PCB设计师犯的错。结果就是过滤器的三个管脚焊盘之间的焊锡短路。

另外,在本例中,过孔与焊盘挨得过近。事实上,过孔的一半已与焊盘重叠。这仅发生在如果通孔的焊盘是在该器件的顶部,而不是在过孔中的情况。记住这个设计禁忌:过孔绝不要与器件的焊盘重叠。

在本例中,过孔侵蚀了元件的焊盘,从而导致焊料漫溢过通孔,使元件翘脱、开路。有几个方法可以扇出此分立元件,以避免这种情况。着眼于面向制造的设计,最好的办法就是使过孔稍稍远离焊盘,且在焊盘和过孔间放置阻焊层。

第二种方法对扇出并非理想。这里,过孔焊盘侵蚀了元件焊盘,而没有放在孔上。结果,当过孔被涂覆时,焊料浸溢过孔壁的可能性降低。有两种方法来解决此问题。第一种是把过孔直接放在焊盘顶部,并对其填充以非导电性填料。第二种方法是使过孔离焊盘再稍微远点,并在过孔和焊盘间放置阻焊层。

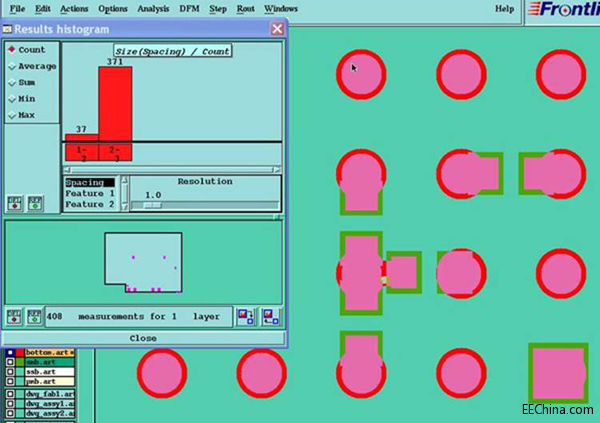

就本具体的高速设计来说,采用了制造商推荐的焊盘模式。问题是,这些建议是针对小批量原型生成,而非批量生产的。焊盘模式是由CAD布局工具创建的,它通过给出器件轮廓以及可将器件管脚焊接其上的焊盘,以便可对PCB上的器件实施焊接,并将器件与PCB固接起来。

但是,当在密度非常高的PCB上,使用大量零部件时,根据组装厂的建议对焊盘模式进行修改就变得极为重要。

再有就是开孔尺寸问题。它必须在0.3mm以下,以便过孔可在回流工艺的刚一开始就被封闭。理想情况,最好是过孔由导电材料封闭,但这从未出现过。对于散热孔,0.3mm间距甚至更细是非常必要的措施,以防止焊料通过孔壁漫爬流溢。

在我们的高速设计例子中,据我们测量,OEM用的过孔约15mil(1mil=0.0254mm)大小,但理想情况是应小于8mil。因为过孔尺寸不对,在生产时,因孔径过大,焊料沿孔壁漫爬溢出。这导致在该PCB设计中,对独立SOP封装产生吸抽作用,致使外设焊盘短路(图3)。

图3:因孔径过大,焊料沿孔壁爬溢流出。导致对独立SOP封装的吸抽作用,致使外设焊盘短路。

在本高速设计中,两个焊盘间缺乏足够的阻焊层是第三个DFM问题。在此,焊盘挨得非常近。结果就是,阻焊层太薄,且在整个工艺流程中都脱离掉了。结果是,焊料呈毛刺状从一个焊盘流到另一个焊盘。后果就是,由于这条不期而至的编外毛刺,该分立元件的焊盘定义变得不一致均匀,如图4所示。处理结果是,将该器件的焊盘变大。

图4:阻焊毛刺。

该设计的另一个焊盘问题是焊盘大小的不匹配,这次是在布局的电源部分。此设计使用了很小的0402(0.4mm×0.2mm)无源器件封装,在电源设计中,不推荐使用这么小的封装。在此,聪明的PCB布局工程师会选用0603厚膜贴片电阻(1608公制封装)、或0805厚膜贴片电阻(稍大的公制2012封装)。但更小就不合适了。

这样谨慎作法是基于这样的考虑:大多数电源布局在外层具有较大的铺铜。在采用了0402封装的本高速设计实例中,0402封装的一端直接连接到铺铜。另一端则只有一条导线和过孔。这样,在回流时,铜箔起着散热器的作用,从而在焊盘的一侧生成一个冷焊点(虚焊)。为了缓解此问题,最好是在焊盘与铜箔间建立热连接。但更好的方法是使用更大封装。

在可制造性设计(DFM)中,PCB设计布线工程师会很容易地忽略咋看起来不那么重要的关键因素。但在后继流程,这些因素在制造过程中发挥着重要作用,可能成为不佳良率的根本原因。

当涉及高速PCB设计,特别是高于20GHz时,若PCB设计和制造团队间缺乏沟通和/或彼此产生错误的预设和解读,就可在制造过程中导致代价高昂的失败。以下列举了一些沟通出问题时的真实情况,并就如何避免此类问题给出了一些建议。

情景1:缩小焊盘尺寸以匹配线宽

在此例,PCB设计师缩小了焊盘尺寸以匹配线宽。他虽没有三思而行,但这种作法完全可以接受。不幸的是,他缩小的太多了,以致成为一个违反IPC(国际电子工业连接协会)约定和制造规则的灾难。

其结果是在制造过程中,出现一系列问题;特别是如图1所示的翘脱(又称墓碑效应,tombstoning)现象的发生。翘脱是发生在PCB焊装阶段的一种器件焊接缺陷,由回流过程中焊料的表面张力所引起。其现象是:器件的一端翘脱、凸起、支离于PCB的铜焊盘,类似一个突起的墓碑。

图1:翘脱

这是因为导线与焊盘粗细一样,所以焊料流入导线,且在回流期间焊料有移动。其结果就造成焊垫大小的不匹配。加上其它DFM问题,使良率低于60%,远低于预期的90%。

其它DFM问题有:

* 批开放阻焊(gang relief mask)工艺造成的焊料短路

* 使用热通孔造成焊料沿孔壁溢流

* 两个焊盘之间阻焊不充分

实际上,PCB设计者使线宽粗细等同焊盘大小的决定,着实无可厚非:在任何高速信号链路中,当信号路径的几何形状改变时,会发生阻抗不连续的情况,从而导致信号路径阻抗的改变。通过使用相同粗细的线径和焊盘,信号通路的几何形状不会改变,当导线接入分立元件的焊盘时,阻抗的不连续问题得以缓解。这在理论上是成立的。但在实践中,当导线太细、焊盘太小时,仍采用两者相同的策略,则会产生翘脱等其它类似的制造性问题。

具体地,在本例,扇出导线与焊盘尺寸相同。此处,采用一个BGA封装,其BGA焊盘以较粗的导线扇出。如果它不是一个非阻焊定义(NSMD)的焊盘,则焊料就将流入从那些特定焊盘扇出的导线,并会在BGA器件的下方造成焊盘大小不一致,并随后形成冷焊点(虚焊)或空隙,如图所示2。

图2:BGA内的空隙

情景2:射频滤波器问题

本例,高速设计包含一个专用、三引脚SOP封装的射频滤波器。在SOP的引脚间没使用阻焊层,对这些引脚采用的是批开放处理,批开放阻焊(gang relieve mask)工艺是定义阻焊层的一种方法,它约定不对一组管脚进行阻焊。其结果是一组管脚间彼此没有阻焊隔离。这可以是刻意达成的效果,也可能是PCB设计师犯的错。结果就是过滤器的三个管脚焊盘之间的焊锡短路。

另外,在本例中,过孔与焊盘挨得过近。事实上,过孔的一半已与焊盘重叠。这仅发生在如果通孔的焊盘是在该器件的顶部,而不是在过孔中的情况。记住这个设计禁忌:过孔绝不要与器件的焊盘重叠。

在本例中,过孔侵蚀了元件的焊盘,从而导致焊料漫溢过通孔,使元件翘脱、开路。有几个方法可以扇出此分立元件,以避免这种情况。着眼于面向制造的设计,最好的办法就是使过孔稍稍远离焊盘,且在焊盘和过孔间放置阻焊层。

第二种方法对扇出并非理想。这里,过孔焊盘侵蚀了元件焊盘,而没有放在孔上。结果,当过孔被涂覆时,焊料浸溢过孔壁的可能性降低。有两种方法来解决此问题。第一种是把过孔直接放在焊盘顶部,并对其填充以非导电性填料。第二种方法是使过孔离焊盘再稍微远点,并在过孔和焊盘间放置阻焊层。

就本具体的高速设计来说,采用了制造商推荐的焊盘模式。问题是,这些建议是针对小批量原型生成,而非批量生产的。焊盘模式是由CAD布局工具创建的,它通过给出器件轮廓以及可将器件管脚焊接其上的焊盘,以便可对PCB上的器件实施焊接,并将器件与PCB固接起来。

但是,当在密度非常高的PCB上,使用大量零部件时,根据组装厂的建议对焊盘模式进行修改就变得极为重要。

再有就是开孔尺寸问题。它必须在0.3mm以下,以便过孔可在回流工艺的刚一开始就被封闭。理想情况,最好是过孔由导电材料封闭,但这从未出现过。对于散热孔,0.3mm间距甚至更细是非常必要的措施,以防止焊料通过孔壁漫爬流溢。

在我们的高速设计例子中,据我们测量,OEM用的过孔约15mil(1mil=0.0254mm)大小,但理想情况是应小于8mil。因为过孔尺寸不对,在生产时,因孔径过大,焊料沿孔壁漫爬溢出。这导致在该PCB设计中,对独立SOP封装产生吸抽作用,致使外设焊盘短路(图3)。

图3:因孔径过大,焊料沿孔壁爬溢流出。导致对独立SOP封装的吸抽作用,致使外设焊盘短路。

在本高速设计中,两个焊盘间缺乏足够的阻焊层是第三个DFM问题。在此,焊盘挨得非常近。结果就是,阻焊层太薄,且在整个工艺流程中都脱离掉了。结果是,焊料呈毛刺状从一个焊盘流到另一个焊盘。后果就是,由于这条不期而至的编外毛刺,该分立元件的焊盘定义变得不一致均匀,如图4所示。处理结果是,将该器件的焊盘变大。

图4:阻焊毛刺。

该设计的另一个焊盘问题是焊盘大小的不匹配,这次是在布局的电源部分。此设计使用了很小的0402(0.4mm×0.2mm)无源器件封装,在电源设计中,不推荐使用这么小的封装。在此,聪明的PCB布局工程师会选用0603厚膜贴片电阻(1608公制封装)、或0805厚膜贴片电阻(稍大的公制2012封装)。但更小就不合适了。

这样谨慎作法是基于这样的考虑:大多数电源布局在外层具有较大的铺铜。在采用了0402封装的本高速设计实例中,0402封装的一端直接连接到铺铜。另一端则只有一条导线和过孔。这样,在回流时,铜箔起着散热器的作用,从而在焊盘的一侧生成一个冷焊点(虚焊)。为了缓解此问题,最好是在焊盘与铜箔间建立热连接。但更好的方法是使用更大封装。

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- PCB抄板/设计原理图制成PCB板的过程经验(02-04)

- IBIS 模型:利用 IBIS 模型研究信号完整性问题(08-08)

- 巧妙的线路板布线改善蜂窝电话的音质(11-01)

- PCB反设计系统中的探测电路(02-18)