UHF频段无线收发信机前端设计

2.2 外接低噪声放大器设计

由前面的分析可知,要减小系统的噪声就需要在滤波器前加入一级高增益、低噪声的放大器。在对器件的选择上,选择了安华高的HEMT器件ATF-54143,它具有超低的噪声系数和较高的线性增益。

设计放大器的第一步就是使器件在整个工作带宽内及邻近区域内稳定。将放大器等效为二端口网络,则二端口稳定的必要条件可表示为:

只要满足上述条件,LNA就无条件稳定。一般LNA不会在全频段内都稳定,因此需要添加外部电路使其稳定,最常用的稳定措施是加入负反馈。本设计中就是通 过在源级加入电感反馈使器件稳定,偏置点的选择采用了手册推荐的Vds=3 V,Id=60 mA。LNA设计的要点是找到最佳噪声点并进行匹配。对于单级LNA而言,等效为二端口网络其噪声系数可表达为:

![]()

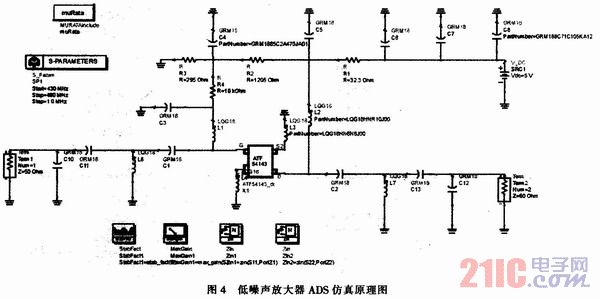

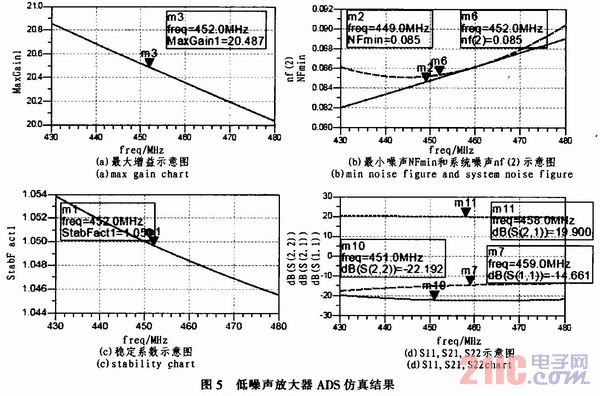

Fmin为LNA管的最小噪声系数,Гs为源反射系数,Гopt和RN分别为最佳噪声反射系数和等效噪声电阻。在LNA设计时就是要将输入端匹配至最佳噪 声点,但有时为了兼顾驻波,增益指标也要进行适当的平衡选择,在宽带设计中为了保证增益平坦度,往往还要加入负反馈等。实际设计在ADS中仿真如图4所 示,输入和输出中都是用π型匹配,仿真结果如图5所示,增益在20 dB,噪声<0.1 dB,实际调试中由于匹配元件Q值,以及电路布线等原因都对噪声产生巨大影响,调试结果在全频段内噪声<1.1 dB。

2.3 锁相环及混频解调部分设计

TH7122内部集成一个整数分频PLL电路,PLL电路是通过一个负反馈回路进行频率合成,其输出频率fVCO是鉴相频率fRO的整数倍N,fR由参考 晶振频率R分频所得。鉴相器将fVCO的N分频信号fN与fR的相位差值转变为电信号经过环路滤波控制VCO产生想要的频率。本设计中参考频率采用10 MHz无源晶振,根据不同接收或发射频率向N和R寄存器中写入分频值。

![]()

混频部分根据芯片设定为下变频,中频设为10.7 MHz。为达到镜像抑制40 dB和较好的信道选择性,设计了一个四频段PIN开关滤波器。该滤波器采用四级电容耦合切比雪夫方式实现,由PIN开关控制接入四级谐振单元的电容变换滤 波器的通频带。每个通频带宽为10 MHz,带外20 M抑制40 dB。4个通频带中心分别为440 MHz,450 MHz,460MHz,470MHz。中频滤波器采用村田公司的CDSCB10M7GA,中心频率10.7 MHz。信号经过中频滤波器后进入芯片内部的中频放大部分,经放大后进入鉴频单元,鉴频器同样选用村田公司的SFECF10M7HAOO,经过鉴频输出 后,将中频信号转换为音频信号,经过Salley-Key滤波后经音频放大器放大输出。

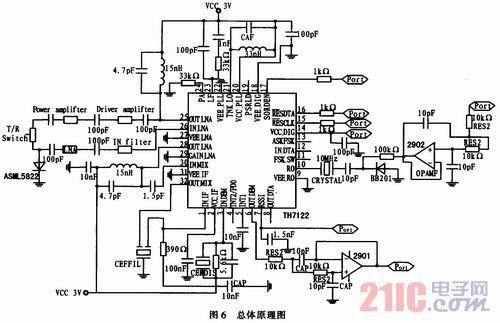

发射信号的调制由于无论是语音信号还是MSK调制信号最终都是在音频范围内的模拟信号,经过实验采用了简单易行的模拟信号经过Sal-ley-Key滤波 后去调制PLL电路使载波产生偏移,实现调制。因为无源晶振需要外接1个负载电容接地工作,电容的变化会引起晶振工作频率的偏移,故将晶振负载电容分为固 定电容C和变容二极管Dc串联两部分,模拟信号接入C与Dc之间,让模拟电压调制信号控制变容二极管电容,拉动晶振工作频率偏移,从而引起fR变化,最终 间接调制fVCO,实现调制功能。VCO输出经过芯片内部放大器输出5~10 mW。为达到发射功率为5 W,设计中采取由BFG540W匹配设计的驱动放大器和π型衰减结合将功率驱动到50mW,再经过功率放大器RA07M4047将功率放大为5 W以上,经过低通谐波滤波器滤除谐波后发射,图6是总体的原理图。

3 结束语

由于该系统主要应用于音频及低速率MSK通信,对交调和动态范围等指标要求不高。在设计中基于TH7122内部已集成整个收发系统的基础上,为了扩展通信 带宽,提高灵敏度和镜像抑制以及输出功率的要求,增加了外接LNA,镜像抑制滤波器和功率提升电路。TH7122芯片的资料可直接参考手册,在绘制整个系 统的PCB时,参考手册的电路连接和PCB板标准,根据基板厚度和材质计算好50 Ω微带线的宽度,走线尽量避免回型和相互的串扰,加大接地面和上下地的穿孔连接等射频PCB板的基本原则。经过仿真和调试。基本满足了系统需求。

- UHF频段智能型RFID读写器的应用研究(05-01)

- 基于UHF频段RFID技术的虹桥机场出租车管理系统(01-15)

- 小型化盘锥天线的设计与仿真(10-28)

- 一种可手戴RFID标签天线设计(03-23)

- 9种RFID标签天线的设计方案(08-12)

- UHF频段无源RFID读写器系统总体方案设计(10-21)