实时时钟芯片应用设计时必须要考虑的事项

期寄存器除多总线时钟外,与其它寄存器无关。星期寄存器在午夜增加,并从7到1变化。只要在程序中的分配是连续的,程序员可以选定任何特殊的一天作为"1"。在总线复用时钟中,星期天必须是"1",因为星期寄存器用白天保存测试。在先前的午夜变化上,为白天保存的测试在午夜完成了,当测试白天保存功能时这必须说明。

当时钟格式由12小时格式成24小时格式,或从BCD格式变成二进制格式,或从二进制格式变成BCD格式,时间,日期,报警寄存器都必须重新进行初始化。

无格式的二进制计数器时钟有一个单独的寄存器,代表性地是32位,每秒能增加一次。通常,寄存器值00H被认为是某些缺省的时间或日期值。例如,格林尼治时间1970年1月1号00:00:00就是"0点"。寄存器中的二进制值就代表从那一点走过的时间。软件程序必须把32位的二进制值变成可以读写的时间和日期,并且将用户数据转化成二进制值。

Y2K Compliance

FS半导体RTCs 与Y2K相适应,兼容Y2K,或者是不包括对日期敏感的逻辑。一个适应Y2K的时钟有这些逻辑,包括世纪信息(有世纪数字或世纪位),能够正确计算闰年直到2099年,但要求系统软件对世纪进行跟踪。二进制秒时钟没有对日期敏感的逻辑,软件必须计算正确的日期,包括闰年的正确性。

晶振和精确度

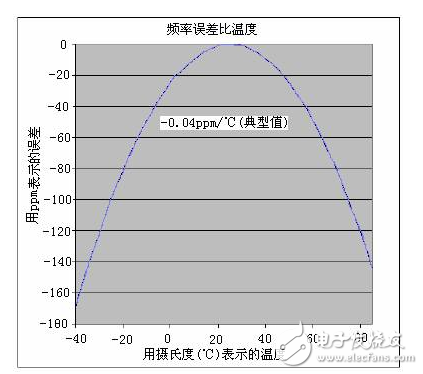

晶振是一种最精确的可以用来提供固定频率的电路。32768Hz的晶振用于大多数RTCs。通过划分晶振的输出频率,一个1HZ的参考频率可用于更新时间和日期。时钟的精确度主要取于晶振的精确度。调谐晶振对温度有一个抛物线响应(图2)。23ppm的误差大约为每月一分钟。

在特殊的容性负载下,晶振能调到正确的频率处振荡。在一个设计能提供6pF 电容负载的晶振的RTC中,用一个调到12.5pF的电容负载的晶振会导致RTC走得要快。

图2.晶振的精确度与温度

晶振的连接

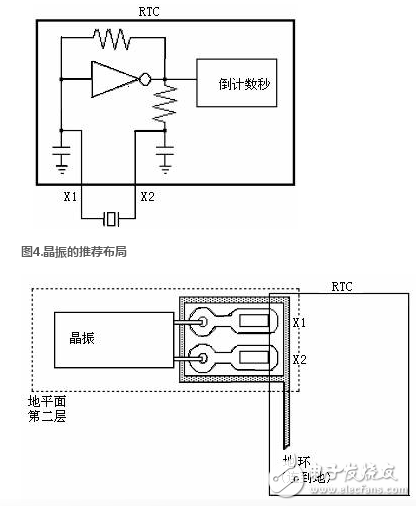

所有FS的RTCs的内部都有一个偏置网络。晶振应直接连到X1和X2的引脚上,而没其它任何元件(图3)。晶振应尽可能近的接近X1和X2引脚。地平面应置于晶振,X1和X2下面(图4)。数字信号线应当远离晶振和晶振的引脚,有严重辐射的RFI的元件应屏蔽起来且远离晶振。低功耗的晶振电路对附近的RFI敏感,RFI会引起时钟走时变快。

图3.RTC-等效电路显示其内部的偏置网络

PC板上包括了可调晶振,例如那些带RTCs,不能把超声波排除在外。晶振可能由共振破坏。

晶振起振时间

晶振的起振时间在很大程度上依赖于晶振的特性和电路布局。高的串行等效电阻(ESR)和过大的电容负载是延长启动时间的主要因素。用含有推荐的特性的晶振和依照推荐的电路布局的电路通常能在一秒内启动晶振。

电池连接

大多数FS的RTCs都包括一个电池输入引脚。电池是用来保持当主电源断开后时钟能够正常走动。对于大多数设计来说,所用的电池都是钮扣锂电池。

有的RTCs用电源电压作为参考来决定什么时候VCC是有效电平。当VCC低于最小值时,器件进入写保护,禁止外部访问器件。当器件工作在VCC条件下时,VBAT输入将处于高阻状态。如果电池没有连接到VBAT上,或是连接到串行二极管,VBAT的输入处于高电平漂浮状态,引起RTC进入写保护。在FS的大多数时钟内部都提供反充电写保护,以消除外部二极管。

读/写时间和日期

由于在读或写的过程中可以进行内部寄存器更新而没数据的破坏,大多数FS 的时钟都提供能确保访问时间和日期的方法。

辅助缓冲寄存器(二级缓存)也用在串行时钟上。当访问(读)RTC时,当前时间和日期传送到辅助寄存器。一个脉冲读信号将从辅助寄存器中读数据,在内部寄存器连续更新时辅助寄存器的内容将保持不变。 下一次访问(当芯片有效,复位或开始)将又一次传送数据。当寄存器被写时类似的过程发生,除非数据在访问之前没有被内部寄存器刷新。

在时间保持非易失性(NV)RAM时钟上,用TE位或R和W位封存用户寄存器。

有多总线时钟里。有几种方法能确保时间和日期寄存器在访问间不变。以下方法即是:

设置位

B寄存器的SET位设为1时,用户双缓存时间和日期寄存器被锁存了。内部寄存器仍然正常的不断更新。

UIP 标志

进程中的更新标志位(UIP)每秒将产生一个脉冲。当UIP位变为高电平后,更新将在244uS后发生。如果UIP位读出的为低电平,为避免更新时的错误用户至少有244uS的时间可以读寄存器的数据。

UF 中断

如果使能,那么在每一次更新周期之后产生一次中断,该周期表明999ms能读有效时间和日期信息。

默认的寄存器值

如果数据手册中没有特殊说明,初始上电寄存器值不确定。也

- 工作在扩展温度范围的计时器件(11-13)

- 工作在高频率的简单锯齿波发生器(05-06)

- Maxim DS3231实时时钟应用笔记、使用指南、FAQ全集(02-14)

- 实时时钟电路设计(05-20)

- 利用SmartCompile和赛灵思的设计工具进行设计保存(04-18)

- 实时时钟芯片DS12887的应用设计(04-23)