所有这些干扰都是从哪里来的?

自从进入市场以来,CMOS 单电源放大器就给全球单电源系统设计人员带来了极大优势。影响双电源放大器总谐波失真 + 噪声 (THD+N) 特性的主要因素是输入噪声与输出级交叉失真。单电源放大器的 THD+N 性能也源自放大器的输入输出级。但是,输入级对 THD+N 的影响可让单电源放大器的这一规范属性变得复杂。

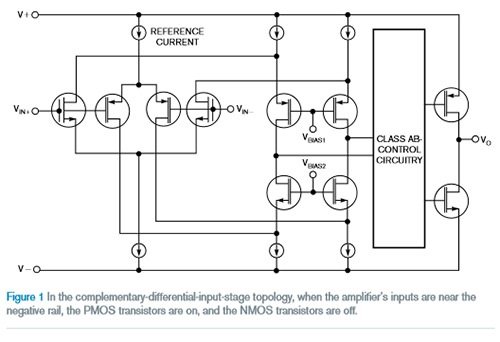

有几种单电源放大器拓扑可在整个电源中接收输入信号。在互补型差分输入级拓扑中,当放大器输入接近负轨时,PMOS 晶体管导通,NMOS 晶体管关断(图 1)。当放大器输入接近正轨时,NMOS 晶体管导通,PMOS 晶体管关断。

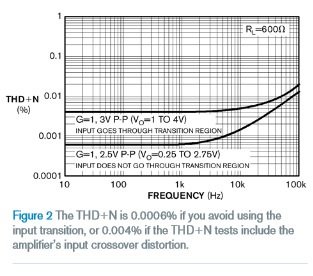

这种设计拓扑在整个共模输入范围内会对放大器失调电压产生极大的变化。在接近接地的输入区域,PMOS 晶体管的失调误差占主导地位。在接近正电源的区域,NMOS 晶体管对成为主导失调误差。当放大器输入穿过这两个区域时,这两个对都会导通。结果就是输入失调电压在两级之间变化。当 PMOS 和 NMOS 晶体管都导通时,共模电压区域大约为 400mV。这种交叉失真现象会影响放大器的 THD。如果将互补型输入放大器采用非反相配置进行配置,输入交叉失真就会影响放大器的 THD+N 性能。例如,在图 2 中,如果不使用输入转换,THD+N 为 0.0006%。如果 THD+N 测试包含放大器的输入交叉失真,THD+N 为 0.004%。您可通过使用反相配置来避免这类放大器的交叉失真。

另一个产生 THD+N 的主要因素可能是运算放大器的输出级。单电源放大器的输出级通常具有一个 AB 拓扑。随着输出信号从一个电轨扫过另一个电轨,输出级也会出现类似于输入级的交叉失真,此时输出级在晶体管间切换。一般来说,通过输出级的较大静态电流可降低放大器的 THD。放大器的输入噪声是造成 THD+N 的另一个因素。高输入噪声、高闭环增益或这两者的存在,都会提高放大器的整体 THD+N 水平。

为了优化互补型输入单电源放大器的 THD+N 性能,可将放大器放在反相增益配置中,并保持低闭环增益。如果系统需要将放大器配置为非反相缓冲器,那就更适合使用具有单差分输入级和充电泵的放大器。

——————————————————————————

FPGA技术资料集锦——那些年,我们为之癫狂的FPGA设计

- 信号链基础知识#69:谨慎增加音频处理系统的THD:如何操作,为什么?(01-06)

- TPS92314 THD 设计考虑因素(二)(01-19)

- TPS92314 THD 设计考虑因素(01-18)

- 为何要谨慎地增加音频处理系统的THD?(01-06)

- 信号链中增加音频处理系统的THD(09-04)

- 信号链基础知识69:谨慎增加音频处理系统的THD:如何操作,为什么?(02-19)