如何为ADC转换器设计变压器耦合型前端

时间:07-11

来源:ADI

点击:

氧体磁珠(在图中示出的是前者),可以消除"电容"项。www.analog.com 网站上的各ADC产品网页中所提供的数据表,示出了无缓冲的ADC在多种频率上的特性。只需点击产品网页上的Evaluation Board链接,就可以选中给出特性阻抗的Excel电子表格。

总之,对输入进行匹配可以给出良好的带宽、增益平坦度(功率驱动的变化更小)和更为出色的性能(SFDR)。

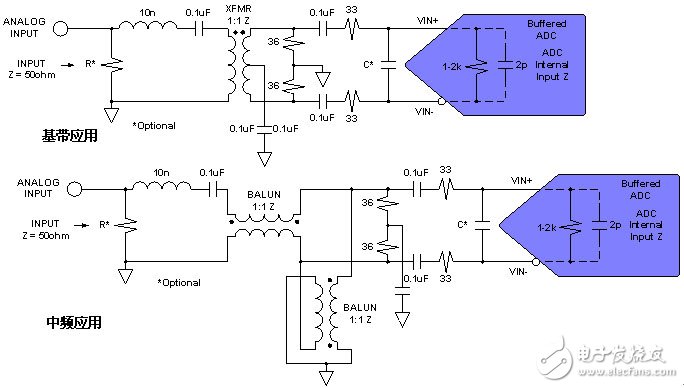

图2 带缓冲的ADC示例

带缓冲的ADC的基带应用同样使用一个简单的网络,类似于开关电容ADC的配置。请注意,应对副边进行端接来将其与原边的输入相匹配。

在图2中,针对高IF应用使用了双balun(平衡/非平衡转换)。这就使得输入在高达300MHz的范围内能得到很好的保持平衡,让二阶失真始终最小化。

小结

设计中必须考虑多种参数,以实现最佳的性能。变压器千差万别。设计者若能理解特定的变压器性能参数,并向制造商咨询没有给出的参数,就能够更好预测出其设计的特性。高IF设计对于变压器的相位非平衡性很敏感;因此这些设计可能需要两个变压器或者balun。

了解所采用的ADC是属于缓冲型还是非缓冲型也很重要。不带缓冲的ADC的输入阻抗是随时间而变化的,在高IF情况下,相应的设计也更为困难。为了优化设计,输入应该实现跟踪匹配。使用磁珠或者低Q的电感来消除开关电容ADC的输入电容分量。这可以最大限度地提高输入带宽,实现更为优化的输入匹配,并维持SFDR性能。缓冲的ADC的设计工作较为方便,即使在高IF下也是如此,但是它们的功耗更大。无论使用何种ADC类型,基带应用的设计工作最简单。

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)