高速面阵CCD KAI-01050功率驱动电路的设计方案

时间:09-28

来源:电子爱好者博客

点击:

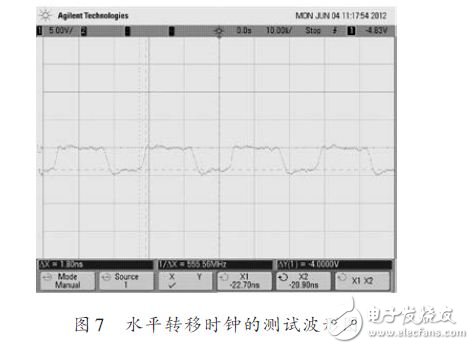

行了测试。图7为水平转移时钟的测试波形图,驱动信号频率为40 MHz,幅值-4~0 V,上升沿与下降沿时间仅为1.8 ns左右,符合CCD驱动时序要求。

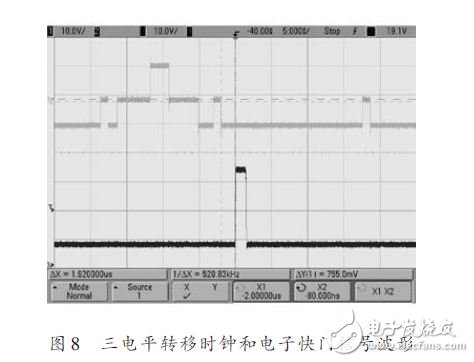

图8 为三电平垂直转移时钟和电子快门是驱动信号波形,图中上面是三电平转移时钟信号,低电平为-9 V,中间电平0 V,高电平12 V;下面波形为电子快门信号,常态电平为6.9 V左右,在计数器计数到需要曝光的时序位置时,输出一个脉冲宽度不小于1 μs的29~40 V脉冲(相机设计值为32 V)。这两个信号其上升沿下降沿时间都很陡峭,满足驱动时序的要求。

4 结语

本文首先介绍了KAI-01050 CCD驱动信号的特点,分析了其功率驱动电路的设计难点,基于本方案设计的重点和难点进行了各种CCD 信号功率驱动电路的设计,并对部分电路进行仿真,验证了设计的合理性。本设计方案已经加工成产品,经实验验证,各部分功率驱动电路满足KAI-01050 CCD 的功率驱动要求,在四通道输出模式下,帧频可达120 f/s,充分验证了该方案的合理性。

- 基于KAI-01050 CCD功率电路的驱动方案(06-10)

- 高速面阵CCD KAI-01050功率驱动电路的设计方案(一)(10-31)

- 用于下一代移动电话的电源管理划分(08-28)

- CCD信号采集系统的USB接口设计(03-12)

- 基于CPLD的线阵CCD驱动电路设计(01-24)

- CCD时代将被CMOS终结?(05-17)