利用数字隔离器优化隔离系统设计

酰亚胺为绝缘体,这种材料也用于许多光耦合器之中。在某些情况下,它们是按照与光耦合器相同的安全标准进行测试,而在其他情况下(如VDE V 0884-10),则专门针对数字隔离器制定了具体标准。例如,表1展示了ADuM140x系列隔离器的机构认证。

其他问题涉及数字隔离器承受过压浪涌的能力,以及它们对共模电压和磁场干扰形式的瞬变的抗干扰能力。幸运的是,借助聚酰亚胺绝缘材料,ADI公司的数字隔离器可以承受最高6 kV的浪涌达10秒。由于隔离栅上只有极低的寄生电容,因此,磁性隔离器相对于其他技术还具有极佳的共模瞬变抗扰度(CMTI)。例如,典型高速光耦合器的CMTI规格为1至10 kV/μs,而磁性数字隔离器可抑制35 kV/μs以上的共模瞬变。

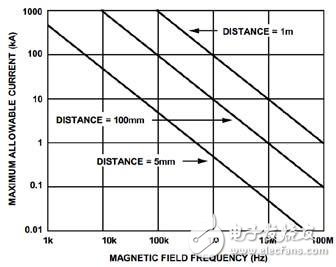

乍一看,对磁场干扰的担心似乎非常合理,因为采用微变压器的隔离器利用磁场来横跨隔离栅发射脉冲。有人可能认为,足够强的磁场可能会干扰脉冲,从而导致输出错误。然而,由于变压器及其空芯的半径非常小,因此只有非常大的磁场或极高的频率才能产生故障。图2所示的最大容许电流和频率仍可以保证AD344x隔离器的输出无故障。例如,只有超过500 A(1 MHz,距离器件 5 mm)的电流才可能触发故障输出。理论上,产生错误输出所需要的幅度和频率组合远远超过了绝大多数应用的范围。

图2.ADuM344x可保证无错运行的最大容许电流和频率

高速运行

当隔离测量系统使用高采样速率时,用光耦合器隔离串行总线可能是比较困难的任务。接收器光电二极管的寄生电容限制了光耦合器传输数字信号的速度。您可以通过增加来自LED的光量来提高该寄生电容的充电速度,但这样做会增加功耗。另外,很少有光耦合器在每个封装内只沿同一方向提供两个以上的通道,而且通常不包括与通道间匹配相关的时序规格。虽然假定同一封装中的光耦合器之间具有良好匹配合乎逻辑,但缺少印制的规格意味着您必须做出工程设计假设。与依赖非印制规格的情况相同,大多数谨慎的工程师会选择留出充足的设计裕量,工作性能远远低于采用单个光耦合器时数据手册指示的性能。

使用数字隔离器的另一优势是,产品可采用4通道器件形式,保证速度最高可达150 Mbps。另外,所有数字隔离器制造商都在数据手册的时序部分提供了保证通道间匹配规格。例如,ADI公司的ADuM344x隔离器在整个工作温度范围内的保证通道间传播延迟失配小于2 ns。实际使用中,这意味着可以在数据手册列出的速度下使用数字隔离器,而无需针对较大或未知的器件间或通道间偏斜来下调系统性能。

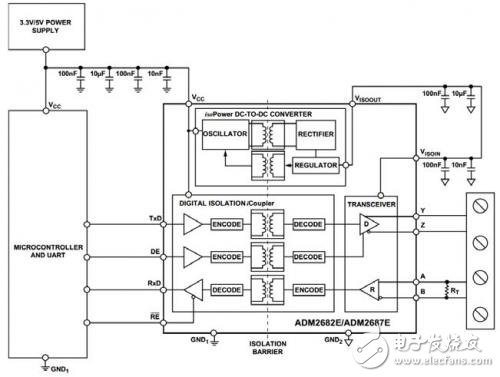

图3.可以用单个ADM2682E实现全双工、隔离式RS-485接口

集成

由于数字隔离器技术兼容标准CMOS工艺,因此,集成额外的功能以简化系统设计相对较容易。例如,传统的热电偶测量器件可能用多个光耦合器来实现低速SPI接口,并用具有驱动器和调节器的隔离变压器来为隔离前端供电。利用集成隔离电源的数字隔离器(如 ADuM5401),整个隔离系统成为带四个数据通道和隔离电源的单个集成电路。与使用分立隔离器和隔离电源相比,这种方式提高了可靠性,节省了大量电路板空间,降低了成本。

许多仪器内置隔离式RS-485端口,用于远程监控或控制。几年前,实现这样的隔离端口不但需要为数据线路配置隔离器,而且需要兼容RS-485差分信号和电源的收发器。图 3显示了像 ADM2682E这样的单个 IC如何将所有功能集成到单个封装之中。

总结

过去,设计隔离式测量设备是一种昂贵、困难、有时甚至令人沮丧的任务,因为光耦合器存在诸多的技术问题。在过去几年中,数字隔离技术的进步大大简化了这一任务。数字隔离技术具有成本低、性能高、易用、集成度高的特点,有助于工程师按时完成开发进度。另外,监管机构认证以及承受高干扰水平的能力使其非常适合工业测量系统中常见的长寿命产品。

- 电容式数字隔离器应用设计(11-05)

- 在系统设计中如何选择隔离器(01-31)

- 在非隔离应用中将数字隔离器用作电平转换器(09-23)

- 电容式数字隔离器的PCB设计及布线设计指南(12-10)

- 电容式数字隔离器在隔离系统中的设计应用(03-07)

- 理解数字隔离器的安全认证(06-17)