双相位锁定回路助力数位中频系统摆脱时钟抖动

时间:02-26

来源:电子发烧友网

点击:

位杂讯水準,c线是外部参考输入相位杂讯的倍频增益产物)

使用低环路滤波器去抖动

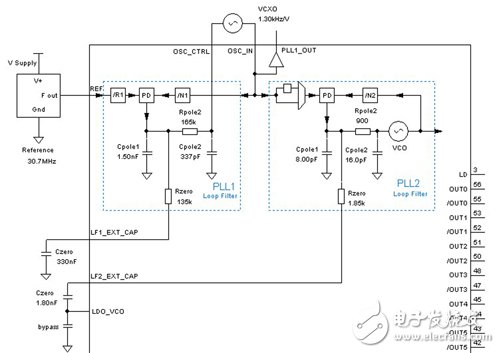

根据上述分析,系统为提高时钟近端相位杂讯水准,就须要提高参考时钟的相位杂讯水准或者降低相位锁定迴路低通滤波器的频率。而在光纤接入数位中频系统中,参考时钟是从光口恢复的,它本身就存在近端相位杂讯(抖动)恶化的问题。如何解决这个矛盾呢?只能从降低低通滤波器频率下手。如图5所示,AD9523在设计中使用了两个相位锁定回路,第一个相位锁定回路接外部的参考时钟(光口恢复的),采取非常低的低通滤波器设置(10Hz~100Hz)。它可以将参考时钟近端相位杂讯良好滤除,而相位锁定回路外接的压控晶体振荡器(VCXO)可以提供很好的近端相位杂讯,这样保证不会因为低通滤波器频率低而将VXCO的近端杂讯抬高(註:这裡对于VXCO来说低通滤波器变为高通滤波回应)。这样第一个相位锁定回路就可以将参考时钟近端相位杂讯很好的抑制。而第二个相位锁定回路采用高频率VCO(3,600MHz?4,000MHz)和70MHz的相位侦测频率。这样可以降低杂讯频率增益的同时,获取更多的频率组合(系统中有时需要不同频率的工作时钟,VCO须要工作在它们的最小公倍数的整数倍)。

图5 双相位锁定回路可滤除相位杂讯并获得良好频率组合。

- 基于EWB的D/A数模转换器的仿真设计方案(06-22)

- 高速数模转换器TQ6124的原理与应用(11-20)

- 压电陶瓷驱动电源特征解析(10-11)

- TLC5615串行数模转换器在开关电源中的应用(05-04)

- 选择和使用高精度数模转换器(05-11)

- 一种典型的高精度数模转换器方案(06-15)