放大器实用设计案例精华汇总(一)

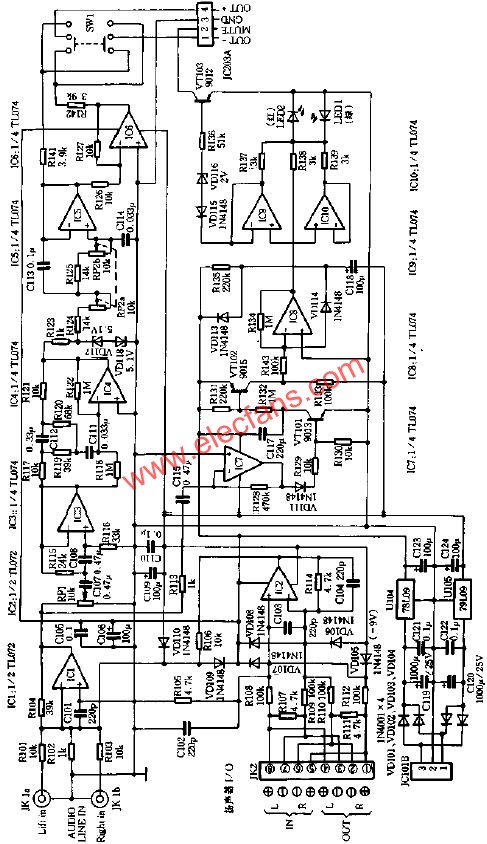

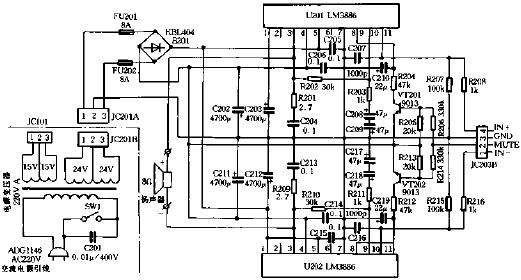

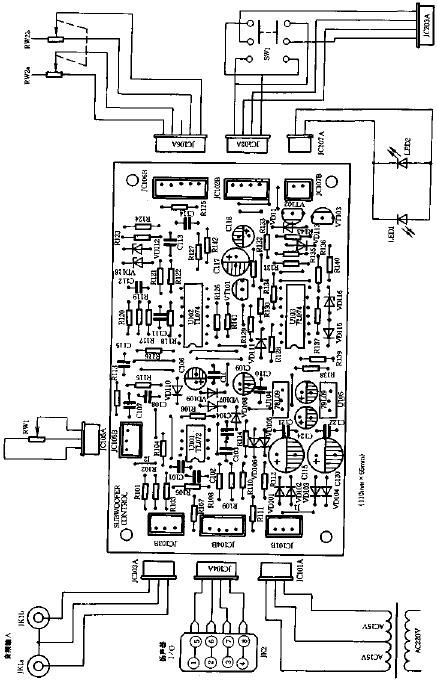

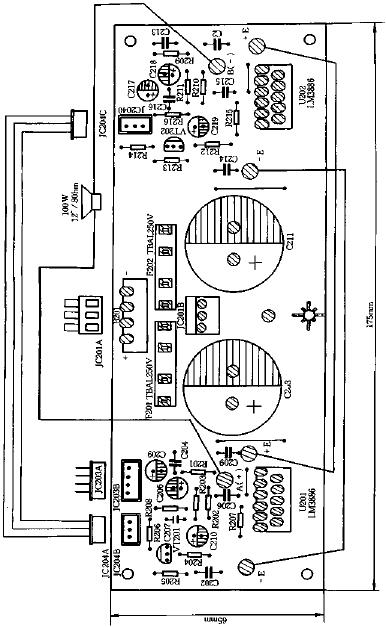

一、功能完善的低音炮功率放大器设计

以往往,超过50W的大功率放大器一般都是采用分立元件来制作。包括近期由日本YAMAHA和SONY等世界著名公司生产的低音炮有源音箱,也都是采用分立元件来设计电路,无可否认,用分立元件制作的功率放大器可达到比较高的性能指标,但其制作成功的难度也比较大,普通业余爱好都多数难以完成。为此,该功率放大器是采用一种集成功放IC与线性运放IC制作的功放性能指标,而且具有完善的保护功能,很适合音响爱好都自己制作。

电路原理:

二、一种可编程宽带放大器的设计

随着微电子技术的发展,宽带放大器在科研中具有重要作用。宽带运算放大器广泛应用于A/D转换器、D/A 转换器、有源滤波器、波形发生器、视频放大器等电路。这些电路要求运算放大器具有较高的频带宽度,电压增值。为此,以可编程增益放大器THS7001和可变增益放大器AD603为核心,设计一种可编程宽带运算放大器。该电路增益调节范围为-6~70 dB,步进间距为6dB,AGC为60 dB,-3 dB通频带为40 Hz~15MHz。矩阵键盘设置增益值、步进,点阵液晶显示实时电压有效值,人机界面友好,操作简单方便。

2 系统总体设计方案

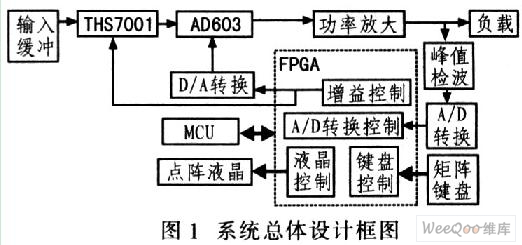

该系统主要由可控增益放大器、功率放大与峰值检波、单片机显示和控制3大模块组成。其中可变增益放大器以THS7001和AD603为核心。单片机控制THS7001实现增益粗调,并通过D/A转换控制AD603实现增益细调,从而使总增益在- 6~70 dB的宽频带范围内线性变化。前置放大器采用由宽带电压型反馈运放THS4011构成的射极跟随器,可有效提高输入电阻;后级功率放大器采用电流型反馈运放AD811,提高系统带负载能力。由二极管峰值检波电路测量峰值,并通过A/D转换、D/A转换实现自动增益控制。通过键盘手动预置增益值,LCD实时显示预置增益值并输出有效值。其系统总体设计框图如图1所示。

3 器件选型及理论分析

3.1 输入级电路运放选型

由于该电路噪声主要取决于第一级放大器。所以选择第一级运放成为决定噪声大小的关键。电压反馈型(VFB)运算放大器具有同相和反向输人端阻抗基本相同(均为高阻),低噪声,更好的直流特性,增益带宽积为常数。反馈电阻的取值自由等特点:而电流反馈型(CFB)运算放大器则具有同相输入端为高阻阻,反向输入端为低阻抗,带宽不受增益影响,压摆率更快,反馈电阻的取值有限制等特点。由此看出,CFB放大器适用于那些需要压摆率快、低失真和可设置增益而不影响带宽的电路;而VFB放大器则适用于那些需要低调电压、低噪声的电路。因此选用电压反馈型运放THS4011作为前级输入。THS4011是一款高速低噪声运算放大器,其带宽为290 MHz,压摆率为310 V/μs,输入噪声为

4.2 峰值检波电路

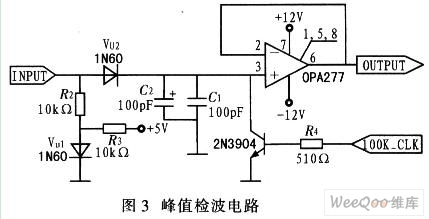

峰值检波电路由二极管电路和电压跟随器组成。其工作原理:当输入电压正半周通过时,检波管 VU2导通,对电容C1、C2充电,直到到达峰值。三极管的基极由FPGA控制,产生1Oμs的高电平使电容放电,以减少前一频率测量对后一频率测量的影响,提高幅值测量精度。其中Vu1为常导通,以补偿VU2上造成的压降。适当选择电容值,使得电容放电速度大于充电速度,这样电容两端的电压可保持在最大电压处,从而实现峰值检波。

该电路能够检测宽范围信号频率,较低的被测信号频率,检波纹波较大,但通过增加小电容和大电容并联构成的电容池可滤除纹波。而后级隔离,则增加由OPA277构成的射极跟随器,如图3所示。

5 系统软件设计

5.1 程序部分设计

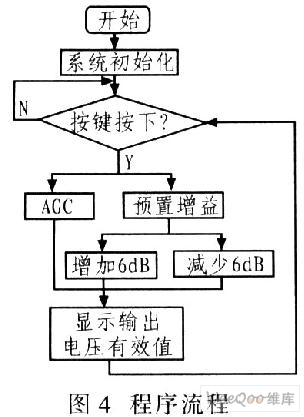

系统软件设计遵循结构化和层次化原则,由一个主程序及若干子程序构成。主程序通过调用子程序控制子程序间的时序,从而使整个程序正常运行。系统软件设计部分由单片机和FPGA组成。单片机主要完成读取键值、控制增益和显示功能。而FPGA则作为总线控制器,管理键盘、液晶和A/D转换器与单片机之间的数据交换。以Ouartus II 7.2为设计环境,用Verilog HDL硬件描述语言编程,完成各功能模块的设计,并仿真测试设计好的各个模块,再将各个模块相互连接。程序以按键中断为主线,以各项功能为分支,图4为程序流程。

5.2 FPGA部分设计

FPGA主要完成A/D、D/A转换器的串并转换。采用12位D/A转换器TLV5618,该器件是串行接口,大大节约系统端口资源,但MCU的P0、 P2端口是并行口,与串行器件的时序匹配较复杂,用静态口P1端口模拟串行口时序又会占用MCU很多处理时间,影响系统效率。

为使MCU对串行器件操作简单,把串行时序在FPGA中用状态机描述,

- 模拟信号隔离应用中隔离放大器设计的黄金法则简介(09-03)

- 一种带有增益提高技术的高速CMOS运算放大器设计(06-26)

- 看一款糟糕的 20W 放大器设计如何毁掉整个扬声器系(06-21)

- 基于NE5532的高保真立体声耳机放大器设计(06-13)

- 一种新型高速CMOS全差分运算放大器设计(06-08)

- 基于Multisim 10的共射极放大器设计与仿真(05-25)