高速电流输出DAC缓冲器

时间:05-13

来源:电子发烧友

点击:

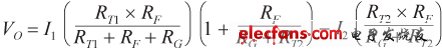

REF1 = VREF1 = 0. 时的关系.为了匹配DAC之外的放大器网络的输入阻抗RT1 和 RT2, 两个端接电阻必须单独设置,同时要考虑放大器的特性.

| (4) |

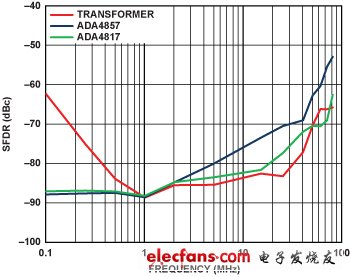

图21比较了放大器在这种配置下的失真以及变压器电路的失真. RT1 = 143Ω, RT2 = 200 Ω,RF = RG = 499Ω, CF = 5pF出于稳定性和高频滤波考虑——且 RL = 1kΩ. 在此ADA4817的性能可与变压器在高频下的性能相媲美,在最高70MHz时,其SFDR可维持在优于-70dBc的水平.与变压器相比,两个运算放大器都能维持出色的低频保真.

图21. DAC、ADA4817和ADA4857的失真 VO = 500 mV p-p

本文讨论了将低失真、低噪声、高速放大器用作DAC缓冲器的一些优势,并将其性能与变压器进行了比较.同时比较了采用两种不同架构的三类应用电路,并以实例展示了DAC和AD8129、ADA4857-1/ADA4857-2以及ADA4817-1/ADA4817-2放大器的测量数据.数据显示,放大器在频率低于1MHz时的性能优于变压器,在频率不超过80 MHz时,非常接近变压器.在权衡考虑功耗和失真时,放大器的选择非常重要.

- ADI实验室电路:如何利用乘法DAC和运算放大器提供可编程增益(02-22)

- 10位电流输出数模转换器DAC MAX5181/MAX51(06-11)

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)