CMOS工艺兼容的热电堆红外探测器

本文实现了一种正面开口的热电堆结构,采用XeF2作为工作气体干法刻蚀工艺释放器件。相对于刻蚀硅,XeF2气体对铝等材料的刻蚀速率极小,这样就可以采用标准CMOS工艺中最常用的材料,如Poly/Al 构成热电偶,从而大大提高兼容性。

1 设计和制作

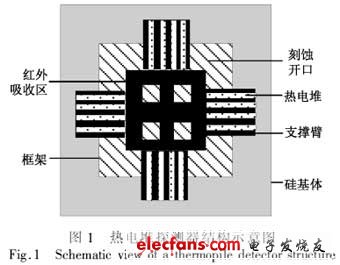

本文提出的热电堆探测器包括硅基体、框架、热电堆、支撑臂、红外吸收层、刻蚀开口六部分,如图1 所示,其中,基体和悬浮于框架中间的红外吸收层分别构成热电堆的冷结区和热结区,支撑臂起到连接框架和红外吸收区以及承载热电堆的目的。支撑臂和红外吸收层是由在单晶硅上淀积的氧化硅和氮化硅复合膜构成。该结构的具体特征是制作了中间悬浮的红外吸收层,并设计了用于干法刻蚀基体的腐蚀开口。由于干法刻蚀的各向同性,腐蚀开口的形状可以多种多样,不同于湿法腐蚀开口必须严格沿着特定晶向排布,从而大大增加了设计的灵活性。

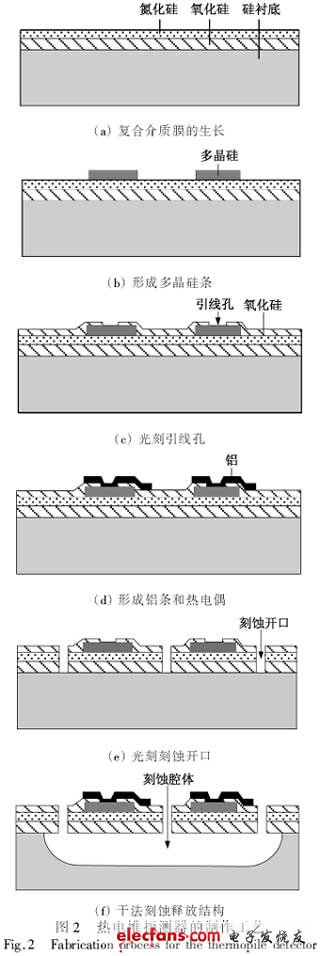

热电堆红外探测器是基于MEMS 技术加工的,工艺步骤如图2,图2 (a)复合介质膜的生长。在抛光的Si 片上,首先热生长氧化硅0.5~0.6μm,再用LPCVD 沉积SiN 0.1~0.2μm,形成氧化硅-氮化硅复合介质膜结构。(b)形成多晶硅条。在复合介质膜上用LPCVD沉积多晶硅(0.8~1.0μm),B离子注入掺杂,退火调整其方块电阻为30~40Ω。第一次光刻,BOE 腐蚀或离子束刻蚀形成多晶硅条,作为热偶的一种组分。(c)光刻引线孔。在(b)中形成的多晶硅上面,淀积一层氧化硅(0.5~0.6μm)作为绝缘层,第二次光刻,形成引线孔。(d)形成铝条和热电偶。溅射Al,第三次光刻,湿法腐蚀形成铝条,进而形成热电偶。(e)光刻刻蚀开口。第四次光刻,形成干法刻蚀的气体通道。(f)干法刻蚀释放结构。工作气体经由(e)中形成的刻蚀开口刻蚀硅衬底,形成悬浮的吸收层,释放热电堆结构。图3 是制作完成的热电堆器件。

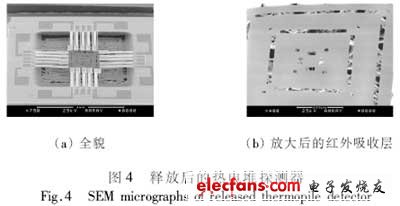

制作完成的热电堆器件采用XeF2气体从正面腐蚀单晶硅衬底,从而形成悬浮膜结构的红外吸收层进而实现器件的释放。影响XeF2气体释放效果的主要因素包括负载,即需要释放的器件结构、器件表面与气体接触情况、器件数目及其在XeF2刻蚀反应腔内的分布状况等和控制刻蚀的各项参数,即刻蚀循环数目、每个循环刻蚀时间及XeF2压力。考虑到实验可行性,本文固定负载,重点研究控制刻蚀的各项参数的作用。为提高实验效率,采用正交实验方法优化释放条件。实验表明,对于本文所提出的器件,特定负载下的优化控制参数为:20个刻蚀循环,每个循环的刻蚀时间为60s,XeF2压力为532 Pa。图4 为成功释放后的热电堆探测器。

2 测试

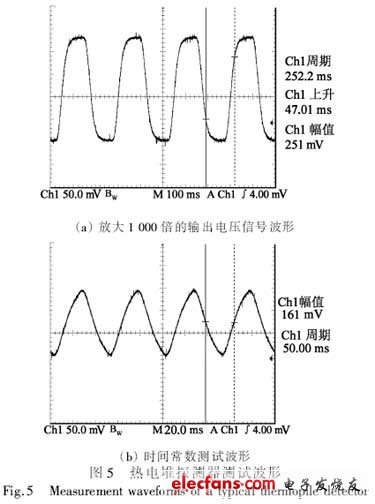

本文所使用的测试系统主要包括黑体作为红外辐射源,光阑用于减弱背景辐射,斩波器用来调制热电堆探测器产生的直流信号、信号处理电路、示波器。图4 中释放后的热电堆探测器通过标有"+ "和"- "号的引脚将直流电压信号接入处理电路的前置放大器。前置放大器的作用是对微弱的传感器信号进行初步放大,方便后续的滤波处理,放大倍数如果太大会在滤波处理之前引入很大的噪声。

表征探测器性能的三个主要指标为响应率、探测率和时间常数。测试结果:响应率13~15 V/W,探测率(1.85~2.15) × 107cmHz1/2/W,时间常数20~25 ms,其中,响应率和探测率通过输出电压来计算,放大1 000 倍后的电压信号如图5 (a)所示。通过调节斩波器的转动频率,使输出电压的幅值达到幅值的1 × 10 - 1倍,此时的上升时间即时间常数,如图5 (b)所示。其他器件参数:几何尺寸2 mm × 2 mm (释放前),热偶对数20,串联电阻16~18 kΩ。通过调整离子注入剂量和能量,可以进一步减小串联电阻,进而提高探测率和响应率。

3 结语

介绍了一种采用MEMS工艺制作的热电堆红外探测器,并采用XeF2气体干法刻蚀工艺成功释放了器件。该方法的优点在于使用干法刻蚀降低了工艺难度,避免了湿法腐蚀的诸多问题,例如,湿法腐蚀溶液不可避免的冲击可能会损坏器件结构,这就限制了器件尺寸,不能制作较大的吸收层,还容易导致结构变形甚至破裂或粘附等问题。另一方面使得腐蚀开口设计更加多样化,进而可以优化探测器的几何构型。正面刻蚀降低了正反对准对光刻机的要求,降低了生产成本。本文所介绍的探测器所有结构都是由标准CMOS工艺中最常见的材料构成,便于将模拟放大器等后端信号处理电路整合到传感器中,真正实现集信号产生和处理于一体的MEMS系统。

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 新型BiCMOS集成运算放大器设计(04-26)

- 一种带隙基准电压源的设计与仿真(09-20)

- 光纤传输系统前置放大器设计(08-07)

- 一种高性能红外信号检测开关的设计与实现(05-27)

- 12位串行A/D转换器MAX187的应用(10-06)