基于AD9959的多体制雷达信号源的设计

1引言

随着雷达技术的发展,出现了多种体制的雷达,比如脉冲多普勒雷达、SAR、相控阵雷达先进,虽然这些雷达的功能不同,但是为了提作用距离和距离向上的分辨率,都彩了大时宽积信号。在雷达信号源设计领域,DDS技术和器件已经得到了很大的发展,相应的出现了很多性能优异的DDS器件,本文旨在介绍一种基于ADI公司的AD9959设计的新型多体制的雷达信号源设计方法,该器件具有稳定度高,相位、频率和幅度调整灵活,能够同时产生4路相关信号,信号形式可以任意设定的特点,这些优异的性能在雷达信号源的研制方面都表现出了良好的应用前景。

2 系统硬件设计

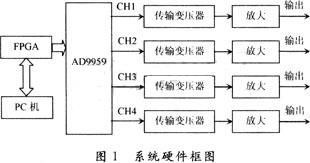

本文设计的多体制雷达信号源是以ADI公司的AD9959为核心,结合FPGA控制电路、信号放大电路构成的。信号参数由主控计算机通过串口进行发送,并同FPGA进行接收,从而控制AD9959完成相应的信号输出。由于在雷达的实际发射过程中,大部分采用的是大时宽带宽的脉冲信号,因此在系统硬件设计的架构中,FPGA还完成了一定的脉冲输出功能,对AD9959输出的连续波信号进行脉冲调制,从而达到输出雷达脉冲信号的能力,而输出的中频信号经过混频电路就可以达到雷达发射所需要的频段。

2.1 AD9959芯片简介

AD9959是一款性能优异的DDS芯片,主要体现在以下几个方面:

4路同步输出通道;

各个通道有独立的频率/相位/幅度控制功能;

超强的通道之间隔离度(>65 dB);

线性频率/相位/幅度扫描能力;

能够达到16级的频率/相位/幅度调制能力;

可通过硬件/软件控制节电模式。

AD9959通过串行I/O提供了多种配置功能,基于这种串行I/O提供的一种SPI模式,同以往的ADI的DDS器件是兼容的。同时,器件采用先进的设计技术,使器件不仅具有优异的性能,而且又具有低功耗的特点。器件集成了具有突出的宽带和窄带SFDR特性的4路高速10位DACs。每一个通道,都具有32位频率控制字,14位相位控制字,10位输出幅度控制字。REF CLK最高可以达到500 M/s,PLL倍频器可以通过软件编程在4~20之间设定。正因为AD9959具有能够输出多通道相关信号的能力,所以AD9959可以广泛地应用于各种场合。

2.2 系统构成

用户通过计算机将所产生信号的参数传送给FPGA,FPGA接收到相应的参数后,控制AD9959输出相应的雷达信号,由于AD9959输出信号是差分电流信号,因此在系统设计时,采用1:1传输变压器将差分的电流信号转化为单端的电压信号,同时为了提高系统的输出驱动能力,在变压器后面进行了信号放大,系统框图如图1所示。

2.3 系统通信接口及协议

系统主要是由FPGA向AD9959发送命令,从而输出相应的信号,对于AD9959的控制主要是通过串行总线SCLK和SDIO来实现的,其中 SCLK的最大时钟速度可以达到200 MHz,AD9959可以通过SDIO的4根数据线(SDIO 0~SDIO 3)同时进行数据传输,从而可以使数据吞吐量变为800 Mb/s,以前ADI公司的DDS产品有并行和串行两种控制模式,比如AD9850,而AD9959这种SPI控制模式,无疑是更加简洁,对于用户控制而言也更加方便。AD9959有4种串行控制传输模式,分别是Single-Bit Serial(2 and 3-wire)Modes,2-Bit Serial Mode,4-Bit SerialMode。AD9959四个输出通道共享寄存器0x03~0x18,这种寄存器地址共享模式,能够使4个通道同时写入控制字。例如要使 AD9959的4个通道都输出某个频率,只需要通过串行总线向AD9959写入一次即可。如果使4个通道互相独立操作,可以通过通道选择寄存器(CSR) 进行选择。

AD9959的串行工作模式都工作于寄存器级传输,而不是字节级传输。但是AD9959提供的SYNC I/O功能可以中断I/O操作,这种模式可以使寄存器的某个字节进行设置,从而减少了设置时间。所有指令都是在SCLK的上升沿写入,而在SCLK的下降沿读出的。在本文所设计的雷达信号源中,对于AD9959的控制模式采用了Single--Bit Serial 2-wire Mode,在这种工作模式下,AD9959使用SDIO 0作为数据传输管脚,要使AD9959工作于这种模式,可以将CSR寄存器中的CSR<2:1>设置为00即可。在Single-Bit Serial 2-wire Mode传输模式下,支持MSB优先和LSB优先两种模式。

系统通过FPGA对AD9959进行操作,主要分为两个阶段,第一个阶段为指令周期,在这个阶段把指令写入到AD9959中,在SCLK的每个上升沿写入一个比特,并且这个指令字节规定了将要进行的传输到底是读操作还是写操作,同时包含了寄存器地址;第二个阶段为数据传送周期,主要传送波形参数的控制字。

图中完成的时序逻辑控制主要由FPGA来实现,具体的信号参数是通过上位机通过串口发送给FPGA,因此FPGA还完成了串口收发功能,通过串口,系

- 信号源分析仪工作原理(12-23)

- 信号源结构原理 (12-11)

- 100MHz带宽的经济型矢量信号源新选择(06-11)

- EWB的基本操作方法(02-11)

- 航空系统跳频信号源的方案(08-09)

- 基于ADF4360-4的GPS信号源设计(08-25)