怎样利用PWM实现DAC电路设计

根据确定的硬件滤波器来选择PWM 载波频率,在两个误差源PWM 占空比分辨率和谐波纹波之间存在矛盾。先确定载波频率,再设计滤波器,是使得分辨率不确定性最小的方法。对于LPC824 的PWM 外设,设计12 位DAC 的计算步骤详细介绍如下。

设定PWM 定时器时钟。LPC824 运行时钟高达30MHz,这里我们留出一些裕量,选择10MHz 时钟,周期为100ns。

设定PWM 信号载波频率。考虑将信号的周期设置为可以被4096 整除,这样可以保证步进值为一个整数,保证转换的准确性与简便性。

因此PWM 的载波周期设定在409600ns,这样在每次DAC 的数字代码步进1 时,只需要将高电平持续时间加100ns,即步进一个计数值即可。我们可以轻松地算出PWM 的载波频率为2.44KHz。

计算硬件低通滤波器所需的衰减倍数,PWM 信号的交流分量中,基波频率最低,当占空比为50%时,基波的幅度最大,若这种情况下滤波器能将基波幅度衰减至1/2LSB 之下,则在所有占空比情况下,都可以将PWM 信号的交流分量衰减至1/2LSB 以下。因此可根据50%占空比时的基波幅度,计算所需的衰减倍数。

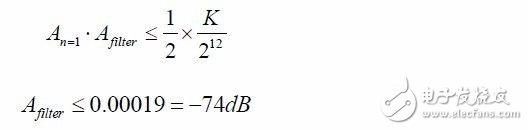

首先需要将n=1 代入公式(6),得到基波的幅度An=1:

然后,计算使得基波幅度小于1/2LSB 的衰减倍数Afilter。

总结实现12 位DAC 分辨率的计算过程,LPC824 的PWM 时钟设置为10MHz,载波频率设置为2.44kHz,硬件低通滤波器需将2.44KHz 频率分量衰减74dB 以上。

>>> 3.2.2 有源低通滤波器

在PWM 实现DAC 应用中,带宽、阻带滚降速率是两个重要的滤波器性质。滤波器带宽定义为幅频响应等于0.707 倍时的频率。滤波器带宽直接揭示了最大信号带宽,即PWM 方式DAC 能够有效处理的最大信号频率。阻带滚降速率是高频部分幅频响应曲线的斜率。带宽、滚降速率共同决定滤波器输出端看到的谐波纹波幅度。

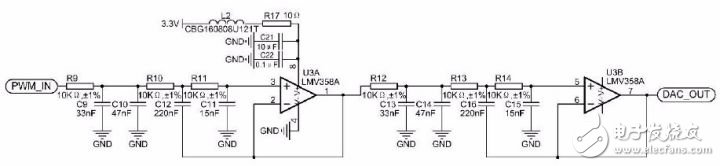

通常低通滤波器为-20dB 每十倍频程每阶滤波器,若低通滤波器带宽设置为载波频率的1/10 频程,即0.244KHz,衰减-74dB 至少需4 阶低通滤波器。综合考虑带宽、滤波器电路的复杂程度,低通滤波器带宽设定在200Hz,使用两级3 阶巴特沃斯低通滤波器级联形成6阶滤波器,详见图 3.6。

图 3.6 6 阶巴特沃斯有源低通滤波器电路

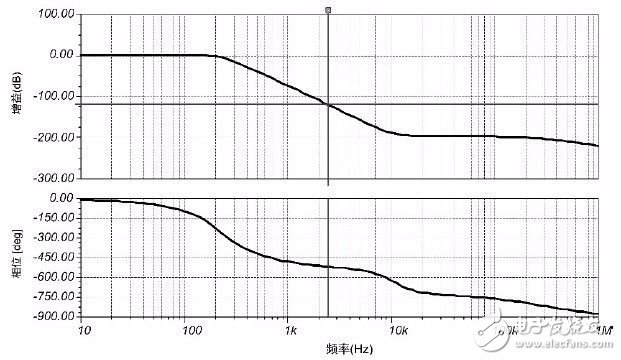

此滤波器电路的幅度曲线详见图 3.7,2.44kHz 频率成分衰减比例为100dB 左右,具有足够的裕量。如果只需用到10 位分辨率DAC,可只选择使用第一级滤波器。

图 3.7 6 阶有源低通滤波器幅频曲线

与LPC824 的ADC 信号输入滤波器类似,这里再次使用单运放的三阶滤波器电路拓扑,避免常规有源滤波器电路设计对运放的带宽要求。常规配置需要运放增益带宽积至少比输入信号的最高频率高5 到10 倍,否则当输入信号的频率成分高于增益带宽时,高频成分将直接馈通至输出。根据PWM 信号的最小占空比100ns,主要高频成分可达10MHz,需用到50M~100MHz 带宽的精密运放。这类宽带精密运放非常贵,有时相当于直接使用一个DAC芯片的成本。

而在图 3.6 中,使用3peak 公司增益带宽积仅为1MHz 的通用运放LMV358A 实现同样功能,使得滤波器的成本可接受。

3.3 测试验证

为验证所实现12 位PWM DAC 的有效性,特制作了实际的电路板进行测试,主要测试数据为DNL、INL、建立时间。

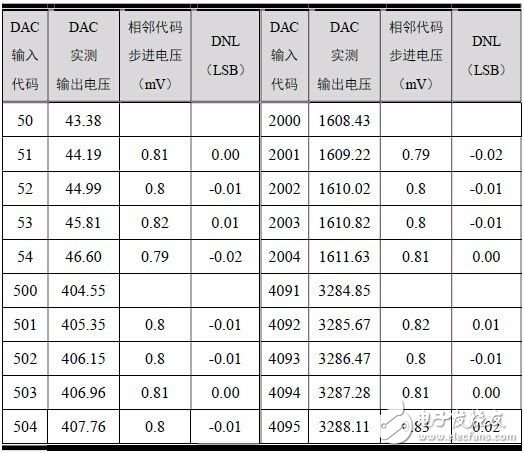

>>> 3.3.1 DNL

DNL 差分非线性定义为任意两个连续数字代码所输出步进电压的实测值与理想值之差。理想DAC 的步进电压为,每次严格步进一个LSB(DNL=0)。

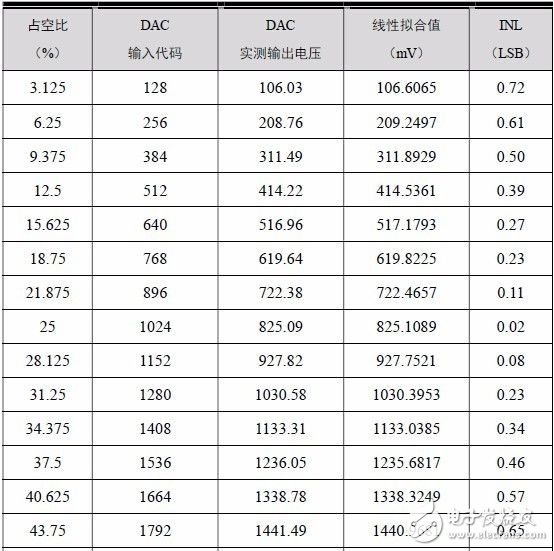

在DAC 输入数字代码范围内,取若干点的DNL 测试验证(1LSB=3.3V/212=0.81mV),数据详见表 3.1。可以看出,DNL 最大值为0.02 个LSB。

表 3.1 PWM DAC 的DNL 测试数据

>>> 3.3.2 INL

INL 积分非线性是表征DAC 精度的一个重要参数。在DAC 的全量程范围内,设置输入数字代码从小至到大,依次等间距输出一系列电压值,可以线性拟合出一条最贴近这些电压值的直线。理想情况下,DAC 是线性的,这些电压值应该全部落在该直线上。实际输出电压值与拟合直线的偏离程度,则表征了DAC 的非线性。

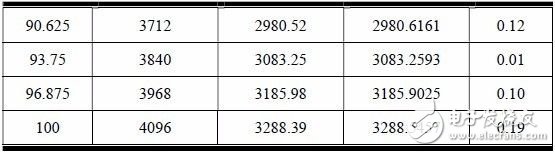

INL 测试数据详见表 3.2,从表中数据可以看出,INL 最大值为1 个LSB。

表 3.2 PWM DAC 的INL 测试数据

>>> 3.3.3 建立时间

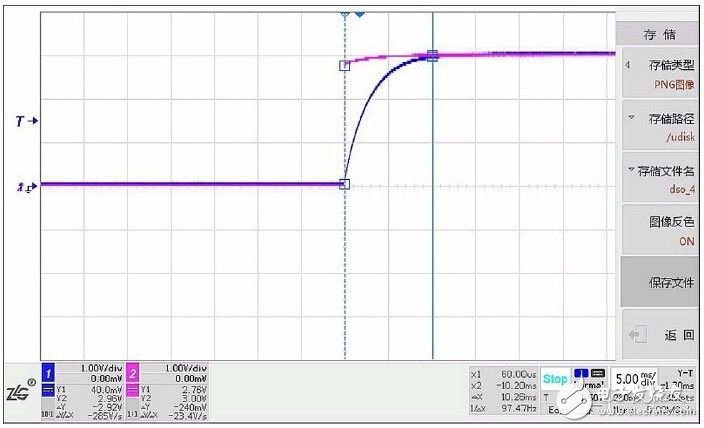

建立时间是指从发出更新输出值的命令,到DAC 输出电压建立到最终值误差范围之内的时间间隔。建立时间受输出有源低通滤波器的带宽等参数影响,测试波形详见图 3.8。

图 3.8 PWM DAC 输出建立时间测试

从上图可以看出,建立时间ΔX 约为10ms。

3.4 参数总结

总结精度指标测试值详见表 3.3,用作对比的AD5623 是

dac 相关文章:

- 选择和使用高准确度数模转换器(08-20)

- 解读高速数/模转换器(DAC)的建立和保持时间(12-06)

- 利用MDACs实现电流电压转换(12-13)

- 现代DAC和DAC缓冲器有助于提升系统性能、简化设计(02-24)

- 双通道 LTC2644 使用经验谈(附原理图)(05-17)

- Xilinx SDAccel 环境:为数据中心带来最佳单位功耗性能(10-26)