LPC1754内部PLL0原理及应用设计详解

LPC175x作为NXP公司主推的cortex-M3内核芯片,广泛应用于各工控、电子计量、报警系统等领域,无论何种应用,根据实际需求选择合适的时钟源并配置合理的系统时钟频率都是必不可少的。

振荡器

以EasyARM-1754M3开发板为例,LPC1754芯片外部晶体振荡器包含两个,一个频率为12MHz外部高速晶振和一个频率为32.768KHz的外部低速晶振,两个都可以使用软件设置选用或不选用。此外LPC1754内部也包含三个独立的振荡器,他们分别是内部主振荡器,内部RC振荡器和内部RTC振荡器。实际应用当中常用的振荡器是外部高速晶体振荡器,和外部低速晶体振荡器。

LPC1754内部PLL0原理简介

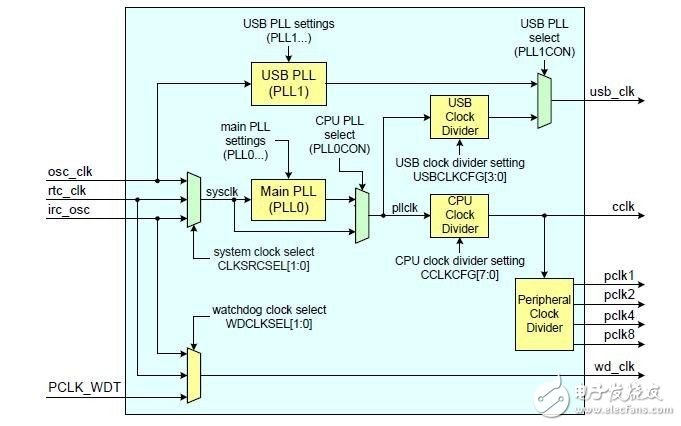

PLL0包含多个寄存器,其中PLL0时钟源的选择可在CLKSRCSEL寄存器中设置,PLL0将输入时钟进行倍频,然后再分频为CPU及芯片外设提供实时时钟信号。PLL0可产生的时钟频率最高可达100MHz,是CPU所允许的最大值。

PLL0内部结构可表示为下图,PLL0的输出时钟信号即为pllclk,后经过CPU时钟分频器的分频,产生系统时钟,系统时钟再进入外设时钟分频器后输出多路的外设时钟。

应用举例

EasyARM-1754M3开发板配套的所有例程使用统一的系统初始化函数SystemInit()将系统时钟配置为96MHz,外设时钟配置为默认值24MHz。用户可在对此函数有一定理解的条件下,根据自身实际需求,对参数进行修改,可修改项一般包含时钟源、倍频系数、分配系数三个重要参数,系统初始化函数当中的PLL0配置部分如下程序清单所示:

#if (CLOCK_SETUP) /* Clock Setup */

LPC_SC->SCS = SCS_Val;

if (SCS_Val & (1 < 5)) { /* If Main Oscillator is enabled */

while ((LPC_SC->SCS & (1<6)) == 0); /* Wait for Oscillator to be ready*/

}LPC_SC->CCLKCFG = CCLKCFG_Val; /* 系统时钟分频值,CCLKCFG_Val值可改 */

LPC_SC->PCLKSEL0 = PCLKSEL0_Val; /* Peripheral Clock Selection */

LPC_SC->PCLKSEL1 = PCLKSEL1_Val;

LPC_SC->CLKSRCSEL = CLKSRCSEL_Val; /* 选取时钟源,CLKSRCSEL_Val值可改 */

#if (PLL0_SETUP)

LPC_SC->PLL0CFG = PLL0CFG_Val; /*PLL0倍频值,PLL0CFG_Val值可改 */LPC_SC->PLL0CON = 0x01; /* PLL0 Enable */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC->PLL0FEED = 0x55;

while (!(LPC_SC->PLL0STAT & (1<26))); /* Wait for PLOCK0 */

LPC_SC->PLL0CON = 0x03; /* PLL0 Enable & Connect */

LPC_SC->PLL0FEED = 0xAA;

LPC_SC-> LPC_

- NXP (Freescale) QorIQ LS1088A-RDB(05-16)

- NXP (Freescale) NOVPEK i.MX6Q/D(05-16)

- NXP (Freescale) QorIQ T1023RDB(05-16)

- 大联大控股品佳推出Microchip、NXP远程医疗解决方案(02-07)

- 飞兆、NXP、TI、安森美四家LED驱动方案大比拼(04-07)

- 最全NXP智能照明解决方案(11-25)