高杂波衰减系统关键性能指标介绍

时间:08-27

来源:FPGA开发圈

点击:

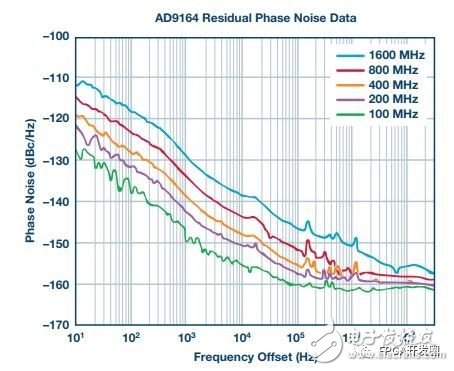

频率受限于稳压器选择。高于100 kHz的频率受限于时钟源。由于使用的时钟是用晶体振荡器倍频产生的6GHz,滚降来自于倍频电路中的RF滤波器,因此高于10 MHz的急剧下降来自于时钟源。

其他的一些DAC频率也使用了提升稳压器性能的残余相位噪声方法进行了测量,图9中概述了部分。这些改进在几个评估板上都做了复现,所有的情况都显示了同样的改进后的结果。

图9. 改进了低噪声稳压器性能的AD9164残余相位噪声测量

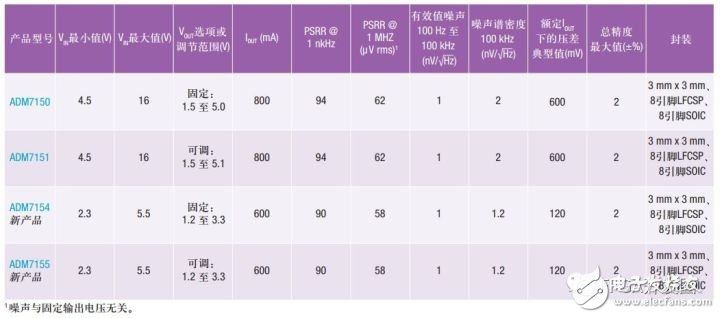

表1. 包含一流的噪声密度性能的稳压器系列

超低噪声稳压器系列的噪声密度相似,如表1所示。正如本文所展示的,稳压器对DAC的相位噪声影响是值得注意的,超低噪声稳压器系列推荐用于任何要求最佳的相位噪声性能的RF系统中。

6

结语

相位噪声基础定义的复习、绝对和残余相位噪声、DAC相位噪声测量测试设置以及稳压器噪声贡献。

本文演示的DAC相位噪声性能改进包含残余相位噪声测量方法和最佳稳压器选择。最终结果是,通过ADI公司的低噪声稳压器系列对模拟电压和时钟电压供电时,AD9164现在可支持超低相位噪声、基于DDS的应用。

- 模拟信号路径在便携医疗设备中的技术要求(11-17)

- 教你如何选择A/D芯片(10-18)

- 细说模拟信号采样与AD转换(11-18)

- 电子电路常见故障类型及处理方法系统解析(08-22)

- CCD模拟输出信号处理电路图(03-03)

- cmos电平是模拟信号还是数字信号(07-26)