一种使用IP方法的独特高效统计计数器应用设计

。该活动在每次通过处理器请求读取后复位存储器位置。

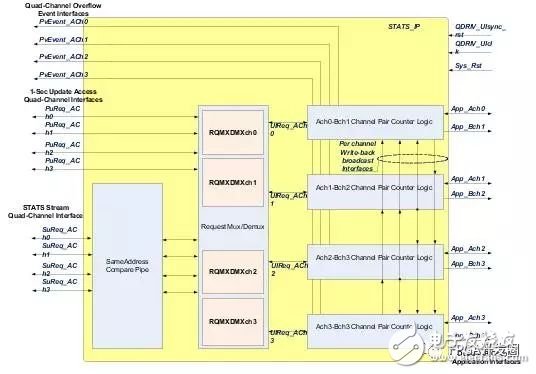

统计IP架构图2中的STATS_IP架构模块图标出了三个子部件:每条通道的同地址比较管道(SACOMP)区块、请求-复用-解复用(REQ_MXDMX_CHn)区块以及每条QDR IV应用通道1个的4个A-B通道配对计数器逻辑(ABCH_CTRL_CHn)区块实例。

图2:统计IP架构

SACOMP模块图包含两个管道阶段,其中一个用于通过比较将同一时钟周期上的所有四条通道进行压缩(SACOMP_ChN-to-All),另一个用于对单一通道上的同一地址进行双向(突发2)比较(SACOMP_B2BChN)。当两条或更多条通道在指定的时间实例中为同一地址时,优先性最高的通道积累地址相同的通道上出现的数据,而所有其他优先性较低、地址相同的通道都将失效。这确保了单一统计请求覆盖所有地址相同的通道,从而预防出现任何数据一致性问题。比较和积累算法对所有可能的情况进行快速评估。此外,在单根通道上,如果有同一存储位置的双向统计更新请求,则最新请求失效,其数据通过之前发生的请求积累。这样能够确保任何同一地址位置的双向存取不会在QDR-IV存储设备定义的读取延迟中发生。

图2所示的请求-复用– 解复用(RQMXDMXChn)区块接收对应通道数的处理器更新请求和统计更新请求。由于处理器更新请求的间隔时间固定,因此RQMXDMXchN选择对应下一个时钟服务的处理器请求,并且通过"请求就绪"回压信号停止统计请求。在开始处理每个一秒更新请求后,RQMXDMXchN停止配置时钟数(默认为10)的处理器请求通道以确保不会提供连续的一秒更新请求服务。停止信号发送至NPU,确保在回压信号失效前不会产生新的请求。该机制能够在不堵塞这一设计的情况下处理统计和处理器请求。

在最终阶段,A-B通道配对计数器逻辑(ABCH_CTRLn)对每项统计请求实施实际的读—修改—写机制,同时确保对每一项处理器请求进行最新读取。该阶段包含读取-延时管道逻辑、控制复用、读写管道和QDR-IV控制器接口逻辑。读写延时管道考虑了内存和控制器延迟。来自邻近通道和同一通道控制复用的反馈机制杜绝所有数据一致性问题发生的可能性。管道中的请求流发起统计和处理器更新。控制复用(CTRL_MUX)区块区分处理器和统计请求,从而使当前数据能够作为处理器读取数据转发或者推送到控制器接口区块以便进行进一步处理。控制器接口区块将实际的读写请求转换为端口A和端口B上的控制器特定命令。

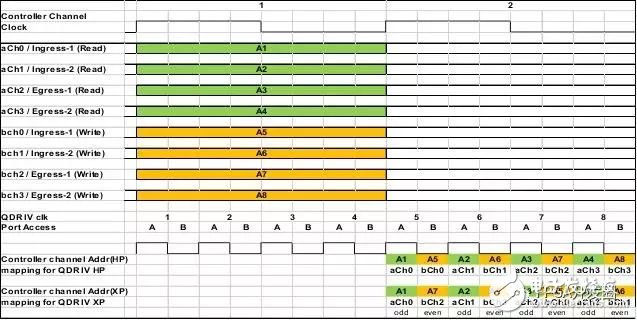

QDR-IV接口运行和应用通道映射统计流四通道和一秒(处理器)更新四通道接口作为应用通道。QDR IV控制器采用带有为QDR IV端口A和端口B定义的专用四通道端口界面的4:1/1:4通道复用/解复用功能。QDR-IV控制器以固定顺序对通道进行复用和解复用,应用端和以4X时钟频率运行的QDR IV设备端之间的顺序为ch0、ch1、ch2和ch3。图3为所假设的QDR-IV控制器顺序和建议的QDR IV HP统计计数器解决方案和QDR IV XP统计计数器解决方案应用通道映射。

图3 QDR-IV接口4:1/1:4 复用/解复用和应用通道映射

在QDR-IV HP统计计数器中,端口A和端口B 的请求独立于地址并按照Ch0-Ch1-Ch2-Ch3顺序的排列。这是因为HP模式无区块要求,并且端口A和端口B上的请求可能包含同一位置的地址。但在QDR-IV XP统计计数器中,端口A和端口B的请求是以奇数-偶数-奇数-偶数为顺序的排列的,这样端口A和端口B在同一时钟周期中就不会出现两个属于同一区块的地址。

基于 QDR-IV SRAM的QDR IV 统计计数器IP为网络流量管理和其他计数器的应用提供了高效的统计计数方案。

- 太阳能发电技术与绿色照明(09-10)

- 一种消防应急灯具专用控制芯片的设计(11-02)

- 基于以太网的可视对讲系统应用(08-30)

- iPad2操控Wifi精确遥控飞行器(10-30)

- 智能视频分析技术应用研究(09-29)

- 低照性能的突破——照亮IP视频摄像机应用前景(11-12)