全新Speedcore标准比FPGA更高效,大幅缩减芯片面积及功耗

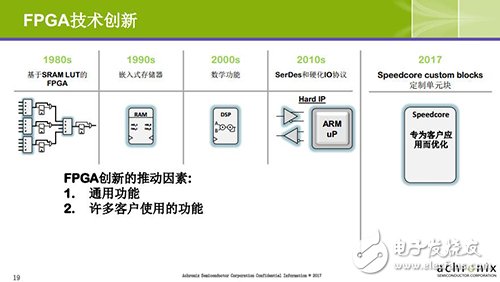

半导体行业中增长最快的领域可以说是硬件加速器芯片,与CPU和GPU有所不同的是,FPGA作为一种典型的非诺依曼架构,是硬件适配软件的模式,能够根据系统资源和算法特征灵活的调整并行度,达到最优的适配,能效比高于CPU和GPU。FPGA不仅在计算的加速具有良好效果,也可以应用于数据中心存储和网络的加速,FPGA可为云服务计算、存储、网络带来综合的提升。今日,作为专注于FPGA技术的Achronix宣布为其eFPGA IP解决方案推出了全新Speedcore custom blocks定制单元块。

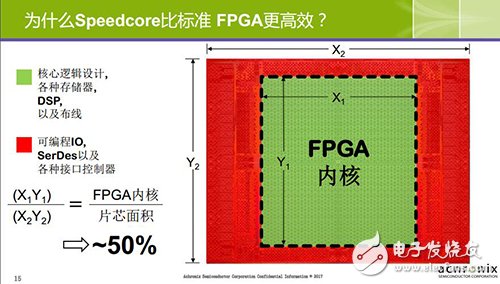

为什么Speedcore比标准FPGA更高效?

随着新一波的智能数据密集型应用的兴起,基于传统的CPU架构已经无法满足这些新应用中计算需求的指数级增长,推动了对全新的、异构的、带有可编程硬件加速器的计算架构的需求。Achronix作为一家私有的、采用无晶圆厂模式的半导体公司,专注于FPGA技术,近几年来营收也在呈现成倍数的增长。在今年,发布了FPGA领域的大动作,第一次在业界推出嵌入式FPGA(embedded FPGA ,eFPGA)产品,Achronix称之为Speedcore。和独立的FPGA芯片相比,嵌入式FPGA功耗更低、成本更低、互联网延迟更低、带宽增加。

Speedcore eFPGA提供了性能最高而成本最低的硬件加速,而现在借助Speedcore custom blocks定制单元模块,过去在独立FPGA运算结构中运行缓慢且消耗大量资源的功能,都可以面向最高性能和最小片芯面积这些目标进行优化。Achronix Speedcore eFGPA嵌入式FPGA可加速数据密集的人工智能(AI)/机器学习、5G移动通信、汽车先进驾驶员辅助系统(ADAS)、数据中心和网络应用; Speedcore custom blocks定制单元块可以大幅度地提升性能、功耗和面积效率,并支持以前在FPGA独立芯片上无法实现的功能。

"业界领袖对Speedcore custom blocks定制单元块及其可发挥的潜力倍感兴奋,"Achronix Semiconductor市场营销副总裁Steve Mensor表示。随后Steve Mensor又接着讲到 "目前与我们合作的公司都在打造下一代异构计算平台和高带宽通信系统,他们正在构建高性能的硬件加速器,可以随着其计算算法的演进而不断调整。现在,Achronix eFPGA IP产品在添加了Speedcore custom blocks定制单元块以后,就使其在拥有可编程性的同时还能够拥有ASIC级的性能以及高片芯面积效率。"利用Speedcore custom blocks定制单元块,客户可以获得ASIC级的效率并同时保持FPGA的灵活性,从而带来了一种可以将功耗和面积降至最低、同时将数据流通量最大化的高效实现方式。

全新Speedcore Custom Blocks定制单元块:大幅度提升性能、功耗和面积效率

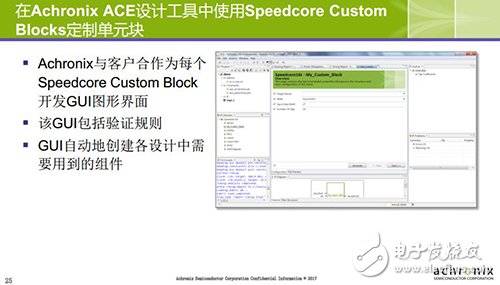

Speedcore custom blocks定制单元块由Achronix与其客户共同定义,这需要一个详细的加速工作负载架构分析,作为性能或面积瓶颈的重复性功能被评估为潜在目标,有可能被硬化而进入Speedcore custom blocks定制单元块。随后,Achronix将为客户提供一个用于基准测试和评估的新版ACE设计工具,它包含了带有定制单元块的、新的Speedcore eFPGA。根据需求,该过程可以被多次迭代,为客户的系统创建优化的解决方案。而Achronix的ACE设计工具全面支持Speedcore custom blocks定制单元块,可以与存储器和DSP单元块相同的方式,提供从设计捕获到比特流生产和系统调试等功能。Achronix为每个Speedcore custom blocks定制单元块创建了一种独有图形化用户接口(GUI),它可以管理所有的配置规则。

ACE拥有Speedcore custom blocks定制单元块所有配置的完整的时序细节,支持ACE去完成各种设计基于时序的布局和布线。客户可以用强大的版图规划器来优化设计,并为所有的单元实例去制定局域或者定点的任务安排。ACE还包括一个关键路径分析工具,它可以支持客户去分析时序。客户还可以使用ACE强大的Snapshot嵌入式逻辑分析仪,去创建复杂的触发器并展示Speedcore内的实时信号。

关于Speedcore嵌入式FPGA(eFPGA)

Speedcore嵌入式FPGA(eFPGA)IP产品可以被嵌入到一款ASIC或者SoC之中,客户通过细化其所需的逻辑功能、RAM存储器和DSP资源,然后Achronix将配置Speedcore IP以满足其个性化的需求。Speedcore查找表(LUT)、RAM单元、DSP64单元和定制单元块能够以灵活的纵列方式组合在一起,为客户的应用创建最优化的可编程功能。

- GPU性能不够跑VR?这项技术或许能解决难题(03-29)

- VR设计:如何实现GPU和显示器高度集成(05-11)

- 基于CUDA技术的视频显示系统的设计方案(06-08)

- 笔记本电脑中温度传感器的应用(06-14)

- 双GPU设计 打造最简单与最快速的加速方案(05-25)

- Intel第六代处理器 Skylake CPU、GPU、主板完全解析(09-06)