经典差动放大器电路设计详解

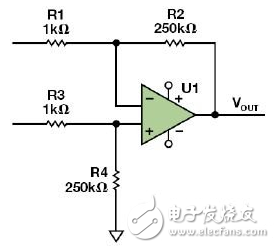

图 4 中的设计用来测量高端电流,其噪声增益为 250。OP07C运算放大器的VOS最大额定值为 150 μV.最大误差为 150 μV &TImes; 250 = 37.5 mV。为了改善性能,采用 ADA4638 零漂移运算放大器。该器件在-40°C至+125°C温度范围内的额定失调电压为 12.5 μV。然而,由于高噪声增益,共模电压将非常接近检测电阻两端的电压。OP07C的输入电压范围(IVR)为 2 V,这表示输入电压必须至少比正电轨低 2 V.对于ADA4638 而言,IVR = 3 V。

图 4. 高端电流检测

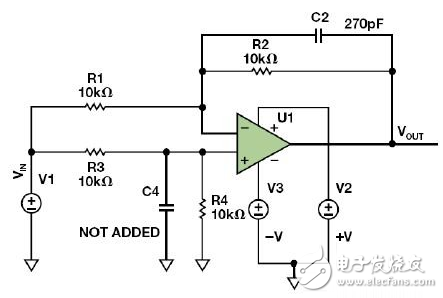

单电容滚降

图5 中的示例稍为复杂。目前为止,所有的等式都针对电阻而言;但更准确的做法是,它们应当将阻抗考虑在内。在加入电容的情况下(无论是故意添加的电容或是寄生电容),交流CMRR均取决于目标频率下的阻抗比。若要滚降该示例中的频率响应,则可在反馈电阻两端添加电容C2,如通常会在反相运算放大器配置中做的那样。

图 5. 尝试创建低通响应

如需匹配阻抗比Z1 = Z3 和Z2 = Z4,就必须添加电容C4.市场上很容易就能买到 0.1%或更好的电阻,但哪怕是0.5%的电容售价都要高于1 美元。极低频率下的阻抗可能无关紧要,但电 容容差或PCB布局产生的两个运算放大器输入端 0.5 pF的差额可导致 10 kHz时交流CMR下降 6 dB。这在使用开关稳压器时显得尤为重要。单芯片差动放大器(如AD8271、 AD8274或 AD8276)具有好 得多的交流CMRR性能,因为运算放大器的两路输入处于芯片上的可控环境下,且价格通常较分立式运算放大器和四个精密电阻更为便宜。

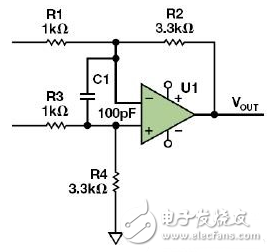

运算放大器输入端之间的电容

为了滚降差动放大器的响应,某些设计人员会尝试在两个运算放大器输入端之间添加电容C1 以形成差分滤波器,如图 6 所示。这样做对于仪表放大器而言是可行的,但对于运算放大器却不可行。VOUT将会通过R2 而上下移动,形成闭合环路。在直流时,这不会产生任何问题,并且电路的表现与等式 2 所描 述的相一致。随着频率的增加,C1 电抗下降。进入运算放大器输入端的反馈降低,从而导致增益上升。最终,运算放大器会在开环状态下工作,因为电容使输入短路。

图 6. 输入电容降低高频反馈

在波特图上,运算放大器的开环增益在-20dB/dec处下降,但噪声增益在+20 dB/dec处上升,形成-40dB/dec交越。正如控制系统课堂上所学到的,它必然产生振荡。一般而言,永远不要在运算放大器的输入端之间使用电容(极少数情况下例外,但本文不作讨论)。

无论是分立式或是单芯片,四电阻差动放大器的使用都非常广泛。为了获得稳定且值得投入生产的设计,应仔细考虑噪声增益、输入电压范围、阻抗比和失调电压规格。

- 浅谈低功耗控制电路和程序设计思路(10-13)

- 基于Zigbee技术的LED灯光控制器的设计及应用(06-27)

- 基于FPGA的全光纤电流互感器控制电路设计(08-02)

- SAM L21微控制器:ARM架构,5种不同模式(03-29)

- T/R组件波束控制测试方案设计(02-18)

- LED大屏幕控制电路设计方案研究(04-23)