高速数字转换器与FPGA开发电路指南

接口目前用于最新转换器。

采用具有JESD204接口的CML驱动器后,转换器输出端的数据速率可达12 Gbps(当前版本JESD204B规格)。此外,需要的输出引脚数也会大幅减少。时钟内置于8b/10b编码数据流,因此无需传输独立时钟信号。数据输出引脚数量也得以减少,最少只需两个。由于转换器的分辨率、速度和通道数增加,数据输出引脚的数量可调整到适应所需的更高吞吐量。由于CML驱动器采用的接口通常为串行接口,增加引脚数的要求与CMOS或LVDS相比要小得多(CMOS或LVDS中传输的数据为并行数据,需要的引脚数多得多)。

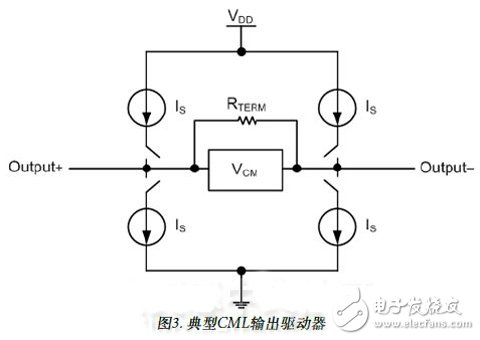

CML驱动器用于串行数据接口,因此,所需引脚数要少得多。图3所示为用于具有JESD204接口或类似数据输出的转换器的典型CML驱动器。该图显示了CML驱动器典型架构的一般情况。图中显示了可选源端接电阻和共模电压。电路的输入可将开关驱动至电流源,电流源则将适当的逻辑值驱动至两个输出端。

CML驱动器类似于LVDS驱动器,以恒定电流模式工作。这也使得CML驱动器在功耗方面具备一定优势。在恒定电流模式下工作需要较少的输出引脚,总功耗会降低。和LVDS一样,CML也需要负载端接、单端阻抗为50 的受控阻抗传输线路,以及100 的差分阻抗。驱动器本身也可能具有如图3所示的端接,对因高带宽信号灵敏度引起的信号反射有所帮助。对采用JESD204标准的转换器而言,差分和共模电平均存在不同规格,具体取决于工作速度。工作速度高达6.375 Gbps,差分电平标称值为800 mV,共模电平约为1.0 V。在高于6.375 Gbps且低于12.5 Gbps的速度下工作时,差分电平额定值为400 mV,共模电平仍约为1.0 V。随着转换器速度和分辨率增加,CML输出需要合适类型的驱动器提供必要速度,以满足各种应用中转换器的技术需求。

随着转换器技术的发展,速度和分辨率不断增加,数字输出驱动器也不断演变发展,以满足数据传输需求。随着转换器中的数字输出接口转换为串行数据传输,CML输出越来越普及。但是,目前的设计中仍然会用到CMOS和LVDS数字输出。每种数字输出都有最适合的应用。每种输出都面临着挑战,必须考虑到一些设计问题,且各有所长。在采样速度小于200 MSPS的转换器中,CMOS仍然是一种合适的技术。采样速度增至200 MSPS以上时,和CMOS相比,LVDS在许多应用中更加可行。为了进一步增加效率、降低功耗、减小封装尺寸,CML驱动器可与JESD204之类的串行数据接口配合使用。

- 编写用于模数转换器的软件驱动程序(08-19)

- 解读高速数/模转换器(DAC)的建立和保持时间(12-06)

- 基于AD73360和TMS320F2812的数据采集系统设计(12-06)

- 双输出电压转换器低成本解决方案(04-26)

- 多相 DC/DC 转换器在整个负载范围内提供了高效率(04-15)

- 一种求解每个热源功率损耗的新方法(08-09)