LED智能照明系统电路模块设计

JTAG是一种国际标准测试协议(IEEEl 149.1兼容),主要用于芯片内部测试。现在多数高级器件都支持JTAG协议。JTAG g路如图3.6所示,这里使用的是20针JTAG接口。各引脚名称及功能如下:1脚为VTrefH标板参考电压,接电源;2脚为VCC电源;3脚为nTRST‘狈0试系统复位信号;5脚为TDI钡IJ试数据串行输入;7脚为TMS、狈IJ试模式选择;9脚为TCK测试时钟:1 1脚为RTCK测试时钟返回信号,不使用时可以直接接地;1 3脚为TDO测试数据串行输出;15脚为nSRSTg[标系统复位信号,与目标板上的系统复位信号(NRST)相连,;4、6、8、10、12、14、16、18、20脚为GND接地;17、19脚未定义。

图3.6中心控制器JTAG电路

为了避免任何未受控制的I/O电平,STM32F103VBT6;(EJTAG输入脚上嵌入了内部上拉和下拉。JINTRST(PB4)内部上拉,JTDI(PAl5)内部上拉,JTMS(PAl3)内部上拉,JTCK(PAl4)内部下拉。(JTAG IEEE标准建议对TDI、TMS和nTRST上拉,而对TCK没有特别建议,但在STM32F 1 03VBT6中,JTCK引脚带有下拉)。

R1、R2、R3均为下拉电阻,令系统复位以后,STM321为部JTAG接口使能,JTAG就可仿真调试。ARM通过JTAG电路与主机的并口连接,先下载程序到FLASHI勾再在器件内通过软件控制程序的运行,由JTAG接口读取片内信息供调试使用的方法进行开发。这种方式不需要仿真器和编程器,大大缩短了开发周期,降低了开发成本。

外围电路设计

STM32具有先进的内核结构和优秀的功耗控制,并且具有性能出众的片上外设。其USB接口可达12Mbit/s,USART接口高达4.5Mbit/s。它采用基于ARMv7.M体系结构的32位标准处理器Cortex.M3,是专门为微控制系统、工业控制系统和无线网络系统等功耗和成本敏感的嵌入式应用领域实现高系统性能设计的。

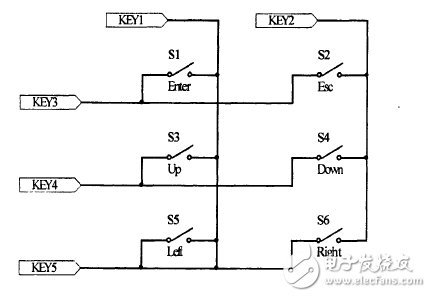

键盘电路设计

图3.7中心控制器键盘电路

本部分采用简单的矩阵式键盘设计,电路如图3.7所示,这样不仅减少I/O UI的占用,而且便于以后的扩展。这里采用行扫描法,进行按键识别。首先,判断键盘中有无键按下:将全部行线(KEY3、KEY4、KEY5)置低,然后检测列线(KEYl、KEY2)的状态。

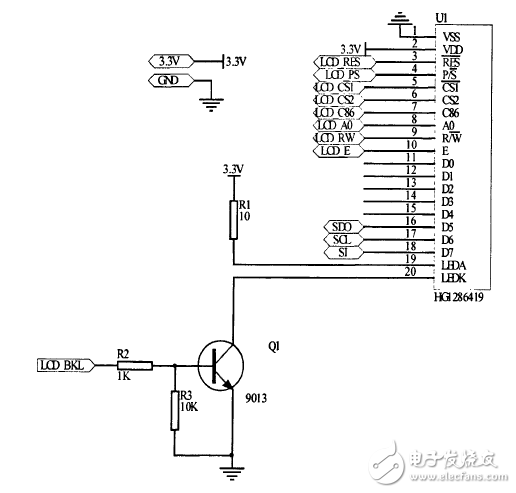

人机界面接口

本系统中的LCD显示模块主要用于中心控制器脱离上位机独立工作时的命令发送与处理。选用清达光电技术有限公司的HGl286419-SYH.LSV型号的图形点阵液晶显示模组,它支持串行和并行两种接口,点阵数为128"64,内置芯片为EPL651 32,可方便的与各种微处理器相连接。

图3.8中心控制器液晶显示电路

LCD模块的接口电路如图3.8所示。其工作电压为3.3V,与STM32SE作电压相同,因此可以直接使用电源电路的输出电压,无需额外电源电路设计。它的显示像素为蓝黑色,显示背景为黄绿色。采用模拟串行通信与ARM芯片连接,连接引脚为SDO(串行数据输出)、SCL(串行时钟)、SI(串行数据输入)分别接蛩jSTM32上的PC9、PC8、PC7引脚上。LCD RES为复位信号,低电平有效。LCD PS用来选择数据传输接口,高电平为并行接口,低电平串行接口。LCD CSl和LCD CS2为片选信号。LCD C86用来选择时序,高电平为6800时序,低电平为8080日‘-j序。LCD A0用来发送数据还是命令,高电平为数据,低电平为命令。LCD RW用来选择读写信号,当为6800时序时,高电平为读信号,低电平为写信号,当为8080Bt序时为写信号。LCD E为6800时序的使能信号或8080时序的读信号。LEDA脚和LEDK脚为LED背光源输入,LEDA接3.3V,LEDK应接地。此处由LCD BKL控制晶体管导通.然后控带rJLEDK的电平。

RS232串行接口电路

本系统采用的是标准的DB.9接口,电路如图3.9所示。由于RS.232.C标准采用负逻辑方式,与STM32F103VBT6的LVTTL电路所定义的高低电平信号完全不同,所以要用SP3232进行RS232电平转换,SP3232的工作电压为+3.0¨5.OV,将EIA/TIA.232电平转换为TTl或CMOS电平。这里有两路串行通信接口,U0和U1。

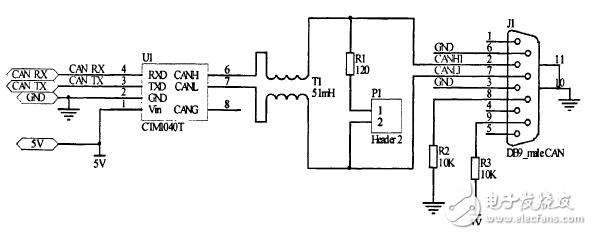

CAN总线通信电路

图3.10中心控制器CAN通信电路

CAN总线通信电路如图3.10所示。由于系统中心控制器要与节点控制器进行通信,因此硬件部分包括CAN通信模块设计,采用CTMl040T是一款带隔离的高速CAN收发器芯片,该芯片内部集成了所有必需的CAN隔离及CAN收、发器件。该芯片的主要功能是将CAN控制器的逻辑电平转换为CAN总线的差分电平并且具有DC2500V的隔离功能及ESD保护作用。T1为高频扼流圈,因为隧道里环境复杂,高频扼流圈可以滤除高频干扰,使电路稳定。

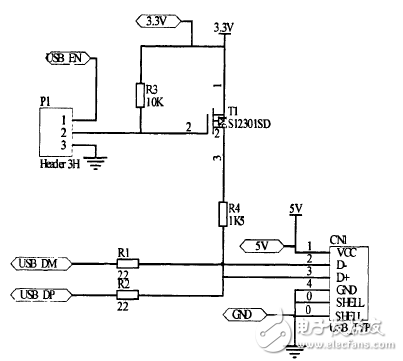

USB接口电路

图3.1 1中心控制器USB接口电路

US

- 盘点:那些为健康而生的APP与智能硬件(11-24)

- 指尖的密码!手指静脉识别鼠标问世(02-02)

- WLAN射频优化的解决方案设计详解(03-03)

- 智能鞋垫:解决跑步者的膝伤问题(02-12)

- 混合动力汽车系统结构大盘点TOP3(03-14)

- 盘点STM32-NUCLEO开发与仿真平台(03-28)