通用串行总线(USB)集线器隔离器电路图

本电路还显示了EOS/ESD保护器件。这些器件选自那些提供各种不同器件的制造商,所选的特定器件允许用0 Ω短路电阻予以代替,以便将其从电路中移除。设计人员应当仔细考虑保护器件选择,包括不需要外部保护到需要全套瞬变抑制器和滤波器元件的各种情况。本应用电路所包括的元件是可以使用的典型元件。

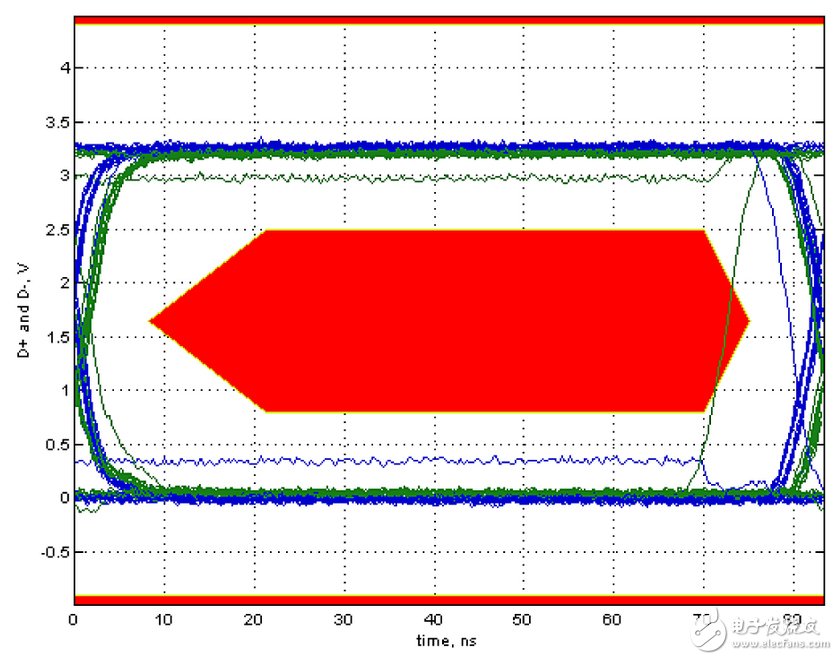

当电路工作时,会进行包检测,并将数据从隔离的一侧传送到另一侧。图2和图3所示的数据分别以时域数据和眼图形式展示了典型的全速处理情况。

图2. ADuM4160上游端口驱动的全速测试包流量

在实时数据中,需要注意的特点是包开始时为无源空闲状态,它会转换为受驱J状态,还有处理结束时的包末尾显示为单端0状态,其后是空闲J状态。正是这种自动控制流和对这些特殊逻辑状态的处理,才使ADuM4160芯片得以实现,并且是市场上独一无二的。

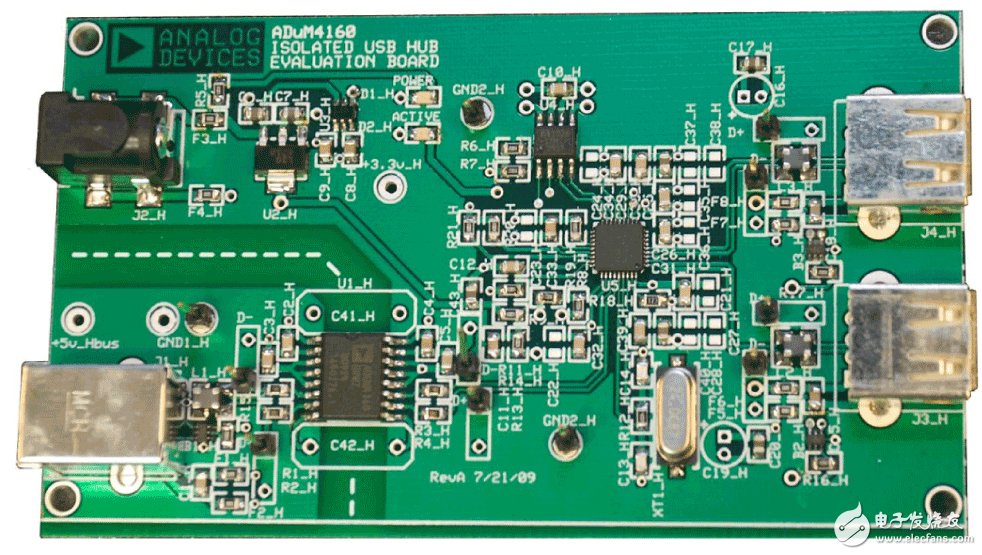

该集线器设计与上游数据连接完全隔离,可承受最高达5 kV的瞬变电压。下游端口通过离线电源供电,以支持全功率应用。低速、全速和高速外设可以任意组合连接到下游端口,集线器控制器根据USB标准正确协商速度。此设计中还包括电流切换和限制功能,还为其它输出保护器件预留了位置,设计人员可以根据需要选择安装。

以下所列为适用的测试参考文件:

上游全速信号质量测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.1节

上游全速上升时间测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.2节

上游全速下降时间测试参考文件—USB 2.0规范第7.1.11节、第7.1.2.2节

图3为全速眼图,显示ADuM4160能够提供充分张开的眼图,并远离禁入区域。但有一个转换是例外,它侵入了禁入区。对于这种测试认证来说这是可以接受的。针对低速评估也获得了类似的数据。评估板的照片如图4所示。欲了解布局文件,请访问: www.analog.com/CN0158_Board_Layout.

图3. 显示禁入区域的全速眼图

图4. ADuM4160隔离USB集线器评估板

- 示波器的LIN、CAN和FlexRay串行总线调试(02-29)

- PIC18F2455/2550/4455/4550之通用串行总线USB(02-04)

- 详细解析串行总线--差分线(差分互连)基本原理及优缺点(03-27)

- 什么是现场总线(06-06)

- 在USB中,定义了这四种类型包(09-09)

- 设计一个属于您自己的简易 I2C 隔离器(05-02)