解读数据中心供电谷歌48V架构布局

谷歌在不断优化并精简其数据中心的供电架构,从最早的定制高效率PSU电源,去掉机房级UPS,将UPS搬到服务器主板上,提升供电效率并减少机房级UPS投资及损耗;随着服务器机柜功率不断增加,以及进一步降低能耗,谷歌转而采用了48V供电架构,在这个方向变化过程中,中间还过度有12V中间转换环节的阶段,直到2013年才实现了从电网到48V再到CPU的极致精简架构,去掉了机房级UPS,去掉了机柜级48V到12V的二次转换,并在服务器主板级实现了48V到CPU的单级变换,最后在2015年最后将铅酸电池替换成锂电池,最终实现了最新的48V整机柜架构。

下图是在OCP峰会上google的48V机柜介绍资料

谷歌48V机柜的布局

谷歌这个半柜高度48V供电整机柜的几个特点:

1、采用48V供电POL架构比起传统的12V服务器架构降低了30%以上的能耗,大大降低了全球云数据中心的能耗;

2、采用了定制的48V供电POL服务器,所有服务器供电均来自整机柜后侧的48V母线排,采用48V母线也可以支撑未来单机柜功率密度增加到50KW以上;

3、将48V电源插框放到机柜顶部,将48V锂电池房到了机柜底部,估计是担心服务器温度影响电池寿命;

4、采用了48V供电的TOR交换机,由两个较小的48V电源给交换机供电,其实可以不用单独配置;

5、POL服务器采用了混搭的方式,部分可能为CPU节点,GPU节点,或者存储节点等任何配置;

6、2U不到高度的PSU插框里边有8个48V的插槽,安装了6个PSU电源模块,考虑5用1备以及UPS充电功率,参考行业典型的3KW高效率电源模块,估计半机柜负荷大约在12到14KW的峰值功率,整个机柜的话两套UPS的功率将翻倍。

7、48V的UPS电池也是模块化设计,可以根据IT功率以及备电时间来选择需要的模块电池数量,上图目视满配可以支持多达10个电池包。

8、谷歌已经大规模使用这个技术好几年了,技术上非常成熟,效率很高,成本也得到很大降低。

谷歌贡献给OCP的48V供电机柜

谷歌贡献给OCP的48V机柜的几个特点:

1、21英寸的内宽,可以支持各种类型的服务器,但可能在机柜深度方面比通用OCP的柜子更短,以便在数据中心内可以安装更多机柜列;

2、可以安装在各种类型的数据中心内,满足各种用户和部署在全球各地的数据中心内使用;

3、冷通道维护,前面两侧可安装网线,或者可选的48V直流PDU;

4、48V UPS插框安装在机柜的中部,大约2U的高度为电源空间(不含电池),配置6个PSU模块,如果采用3KW的典型48V电源模块,则可以支撑最大15KW的机柜功率。

5、由于采用了机柜内的UPS架构,机房级直接采用市电直供,由机柜顶部的母线排直接给整机柜供电,即插即用,供电架构非常简单和扁平,效率和成本较优。

6、如果其他用户的服务器仍然采用12V输入的主板,那也可以通过在这个48V机柜内增加一个48V转12V的DCDC变换器来满足原有12V输入服务器。

7、目前谷歌已经和facebook对这个新的机柜和48V UPS技术准备一个新的规格提交给OCP审批,给行业增加更多的选择。

前面简单分析了该48V整机柜的特点,该整机柜自带48V锂电池BBU,不再需要机房级的UPS,配电结构非常精简,可以大大减低投资和系统能耗,下面我们做个48V整机柜架构和传统UPS供电架构的简单能效对比。

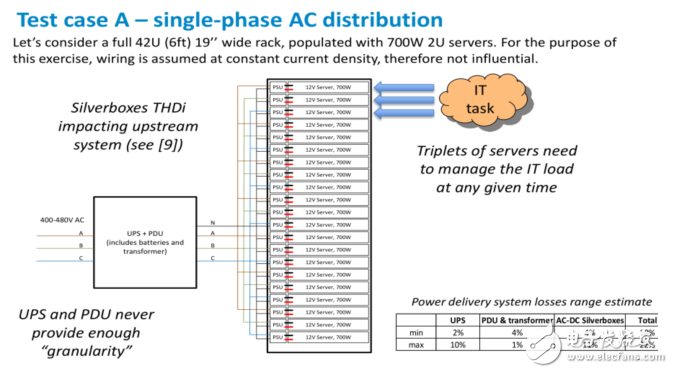

采用传统的UPS供电架构,每台服务器自带PSU电源的传统系统如下图,从电网到12V服务器主板,大约有22%的能耗被浪费了,传统UPS架构下即便采用目前高效率的供电系统,市电到服务器的12V主板也会有6.4%的能耗浪费。

传统UPS供电架构下的供电能效

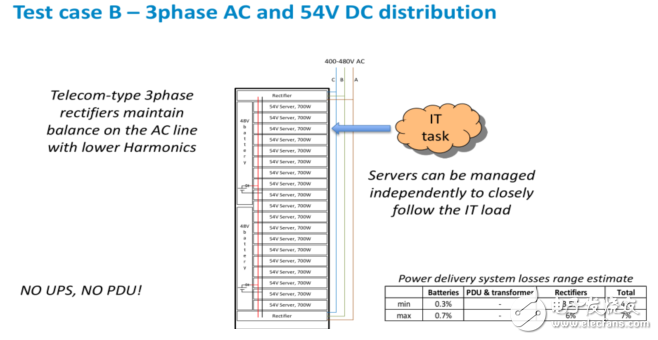

而采用谷歌推荐的48V整机柜供电架构,不再需要UPS和复杂变配电单元,市电直接给到整机柜来供电,市电到服务器主板的典型损耗为7%,目前业界领先水平可以控制在4%以内的损耗。

传统48V整机柜供电架构下的供电能效

因此两者对比下来,采用市电直供48V整机柜带BBU电池包的供电架构比采用传统UPS带12V PSU的机架式服务器供电架构,从电网到服务器主板典型的系统能节能量为15%。

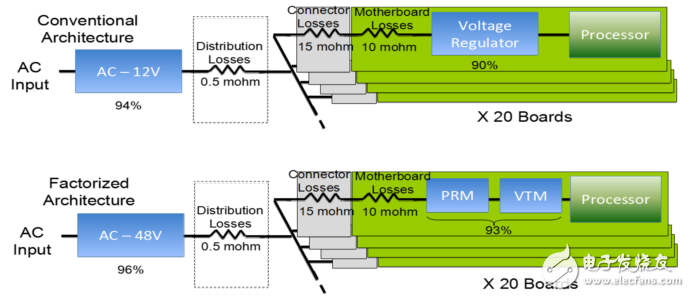

我们再看服务器主板到CPU的供电路径上,采用12V主板和48V主板能耗的对比,这里以数据中心所采用的典型Vicor公司产品为例来计算,分别比较机柜级PSU整流模块效率、12V和48V方案在服务器主板上的传输损耗,以及12V或者48V到CPU、RAM等的降压POL电源的综合效率。从AC-DC电源的输出端经过连接器,传输路径,再经过转换最后输送到处理器。对整体效率来说,传输路径上的损耗也不容忽视。下图是从AC到CPU的全路径状况。

下图为google在OCP峰

- 用于48V电源的完整单IC电源管理电池维护/后备系统(01-15)

- 新一代新能源汽车,为什么青睐48V技术方案(06-13)

- 汽车48V电池系统关键技术及优势盘点(04-18)

- 节油率真的可达20%?详解48V微混系统(09-28)

- 解析48V锂离子电池系统的关键技术及应用现状(04-18)

- 谷歌眼镜的真面目:随时被记录并永久保存(02-18)