射频电路的电源设计要点

(1)电源线是EMI 出入电路的重要途径。通过电源线,外界的干扰可以传入内部电路,影响RF电路指标。为了减少电磁辐射和耦合,要求DC-DC模块的一次侧、二次侧、负载侧环路面积最小。电源电路不管形式有多复杂,其大电流环路都要尽可能小。电源线和地线总是要很近放置。

(2)如果电路中使用了开关电源,开关电源的外围器件布局要符合各功率回流路径最短的原则。滤波电容要靠近开关电源相关引脚。 使用共模电感,靠近开关电源模块。

(3)单板上长距离的电源线不能同时接近或穿过级联放大器(增益大于45dB)的输出和输入端附近。避免电源线成为RF信号传输途径,可能引起自激或降低扇区隔离度。长距离电源线的两端都需要加上高频滤波电容,甚至中间也加高频滤波电容。

(4)RF PCB的电源入口处组合并联三个滤波电容,利用这三种电容的各自优点分别滤除电源线上的低、中、高频。例如:10uf,0.1uf,100pf。并且按照从大到小的顺序依次靠近电源的输入管脚。

(5)用同一组电源给小信号级联放大器馈电,应当先从末级开始,依次向前级供电,使末级电路产生的EMI 对前级的影响较小。且每一级的电源滤波至少有两个电容:0.1uf,100pf。 当信号频率高于1GHz时,要增加10pf滤波电容。

(6)常用到小功率电子滤波器,滤波电容要靠近三极管管脚,高频滤波电容更靠近管脚。三极管选用截止频率较低的。如果电子滤波器中的三极管是高频管,工作在放大区,外围器件布局又不合理,在电源输出端很容易产生高频振荡。线性稳压模块也可能存在同样的问题,原因是芯片内存在反馈回路,且内部三极管工作在放大区。在布局时要求高频滤波电容靠近管脚,减小分布电感,破坏振荡条件。

(7)PCB的POWER部分的铜箔尺寸符合其流过的最大电流,并考虑余量(一般参考为1A/mm线宽)。

(8)电源线的输入输出不能交叉。

(9)注意电源退耦、滤波,防止不同单元通过电源线产生干扰,电源布线时电源线之间应相互隔离。电源线与其它强干扰线(如CLK)用地线隔离。

(10)小信号放大器的电源布线需要地铜皮及接地过孔隔离,避免其它EMI干扰窜入,进而恶化本级信号质量。

(11)不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

(12)PCB板层分配便于简化后续的布线处理,对于一个四层PCB板(WLAN中常用的电路板),在大多数应用中用电路板的顶层放置元器件和RF引线,第二层作为系统地,电源部分放置在第三层,任何信号线都可以分布在第四层。

第二层采用连续的地平面布局对于建立阻抗受控的RF信号通路非常必要,它还便于获得尽可能短的地环路,为第一层和第三层提供高度的电气隔离,使得两层之间的耦合最小。当然,也可以采用其它板层定义的方式(特别是在电路板具有不同的层数时),但上述结构是经过验证的一个成功范例。

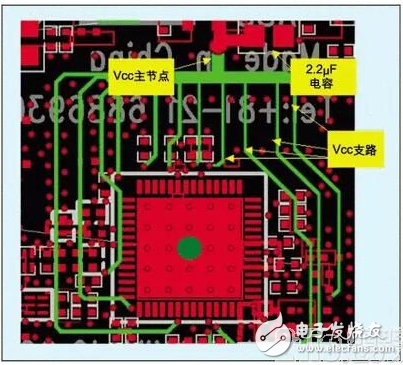

(13)大面积的电源层能够使Vcc布线变得轻松,但是,这种结构常常是引发系统性能恶化的导火索,在一个较大平面上把所有电源引线接在一起将无法避免引脚之间的噪声传输。反之,如果使用星型拓扑则会减轻不同电源引脚之间的耦合。

上图给出了星型连接的Vcc布线方案,该图取自MAX2826 IEEE 802.11a/g收发器的评估板。图中建立了一个主Vcc节点,从该点引出不同分支的电源线,为RF IC的电源引脚供电。每个电源引脚使用独立的引线在引脚之间提供了空间上的隔离,有利于减小它们之间的耦合。另外,每条引线还具有一定的寄生电感,这恰好是我们所希望的,它有助于滤除电源线上的高频噪声。

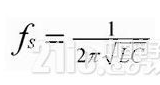

使用星型拓扑Vcc引线时,还有必要采取适当的电源去耦,而去耦电容存在一定的寄生电感。事实上,电容等效为一个串联的RLC电路,电容在低频段起主导作用,但在自激振荡频率(SRF):

之后,电容的阻抗将呈现出电感性。由此可见,电容器只是在频率接近或低于其SRF时才具有去耦作用,在这些频点电容表现为低阻。

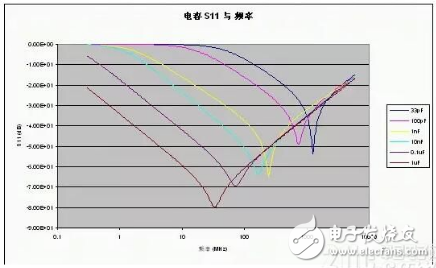

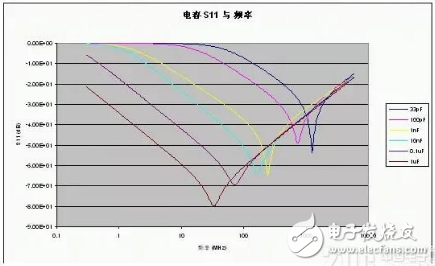

给出了不同容值下的典型S11参数,从这些曲线可以清楚地看到SRF,还可以看出电容越大,在较低频率处所提供的去耦性能越好(所呈现的阻抗越低)。

在Vcc星型拓扑的主节点处最好放置一个大容量的电容器,如2.2μF。该电容具有较低的SRF,对于消除低频噪声、建立稳定的直流电压很有效。IC的每个电源引脚需要一个低容量的电容器(如10nF),用来滤除可能耦合到电源线上的高频噪声。对于那些为噪声敏感电路供电的电源引脚,可能

- 科学掌握无线产品射频电路设计(04-18)

- 射频和数字电路设计的区别(04-26)

- 全面详解射频技术原理电路及设计电路(09-21)

- 一种照明控制开关发射与接收系统的电路设计方案(04-26)

- 相近又有所区别,解析射频和数字电路设计的差异(10-05)

- 如何在PCB板上规划设计好射频和数字电路?(08-06)