电源PCB与layout的29条关系

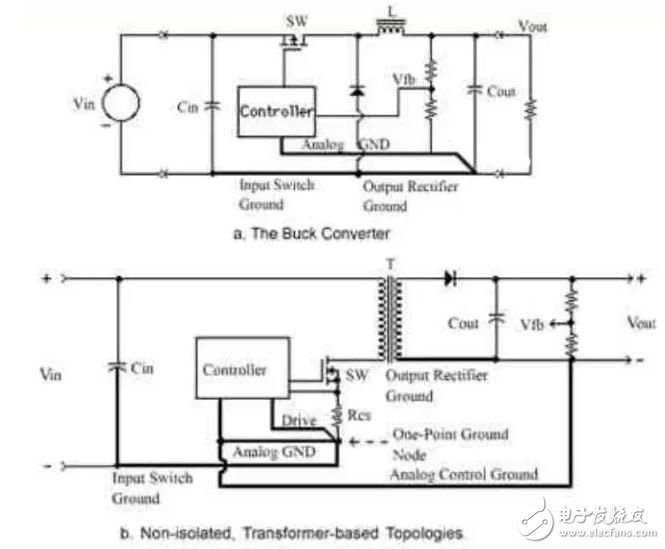

小信号控制地,地的连接方法见如下示意图:

22-29

22、接地时首先应先判断地的性质,再进行连接。采样及误差放大的地通常应当接到输出电容的负极,采样信号通常应从输出电容的正极取出,小信号控制地和驱动地通常要分别接到开关管的 E/S 极或取样电阻上,防止共阻抗干扰。通常 IC 的控制地和驱动地不单独引出,此时取样电阻到上述地的引线阻抗必须尽量小,最大程度减小共阻抗干扰,提高电流采样的精度。

23输出电压采样网络最好靠近误差放大器,而不是靠近输出端,这是由于低阻抗信号比高阻抗信号更不容易受到干扰,采样走线对要尽量相互靠近以减小拾取到的噪声。

24、布局注意电感要远离,并相互垂直,以减小互感,尤其是储能电感和滤波电感。

25、布局注意高频电容和低频电容并联使用时,高频电容靠近使用者。

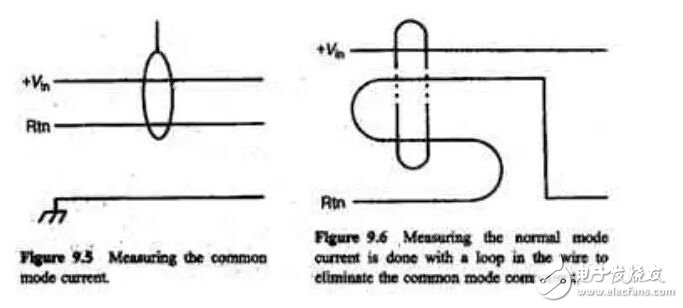

26、低频干扰一般为差模( 1M 以下),高频干扰一般为共模,通常通过辐射耦合。

27、如果高频信号被耦合到输入引线,很容易形成 EMI (共模),可在输入引线接近电源处套一个磁环,如果 EMI 降低就表明存在此问题。解决此问题的方法是,降低耦合或降低电路的 EMI 。如果高频噪声没有被过滤干净而传导到输入引线,也会形成 EMI (差模),此时套磁环不能解决问题,在输入引线接近电源处串两个高频电感(对称),如果 EMI 降低就表明存在此问题。解决此问题的方法是改善滤波,或采用缓冲、钳位等手段减小高频噪声的产生。

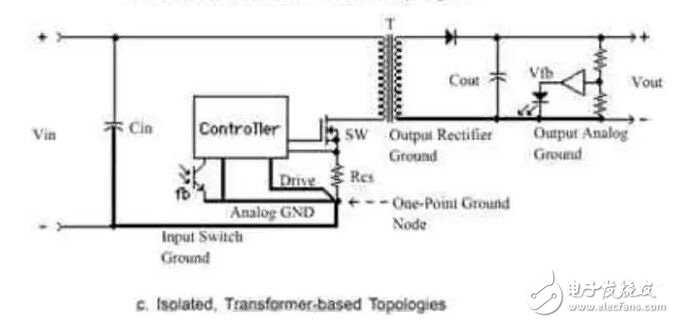

28、差模和共模电流的测量:

29、EMI 滤波器要尽量靠近进线,进线的走线要尽量短,尽量减小 EMI 滤波器前后级的耦合。进线最好用机壳地进行屏蔽(方法如上所述)。输出 EMI 滤波器也要作类似处理。尽量拉开进线和高 dv/dt 信号走线的距离,在布局上要加以考虑。

- 理解pcb layout差分信号(07-14)

- 浅谈开关电源设计中PCB板的设计注意事项(07-08)

- PCB布线技术中的抗干扰设计(03-08)

- 基于Protel 99 SE环境下PCB设计规范与技巧的研究(08-30)

- 高速PCB可控性与电磁兼容性设计(11-18)

- 分布电容在EMC/EMI之设计中的应用(01-11)