内存颗粒涨价狂潮,来了解一下MLC NAND闪存下的技术细节

的是,尽管这种修改允许缩放,但在这个顺序中的某些步骤看起来并不具有任何技术优势。有人不禁会认为,这种方法是否是为了回避其他闪存提供商拥有的STI工艺顺序。

最后,这个器件上几乎20%的阵列聚合物宽度减少应该能降低阵列中的电容性耦合,并改善整体的功率和速度性能。这将进一步确定针对下一代技术节点的工艺,特别是如果低k值材料被用来进一步降低存储器阵列中的耦合。

揭开表象

东芝和IMFT的16Gb MLC NAND闪存器件背后具有不同的细节。东芝在其推出的16Gb、56纳米MLC器件上实现了令人印象深刻的94.5Mb/mm2存储位密度;但是IMFT在其16Gb MC器件上实现了98.7Mb/mm2的密度,已经超过了东芝的存储位密度,并且几乎与竞争对手三星公司的51纳米、16Gb NAND器件的101.7MB/mm2存储密度相当。

再加上IMFT的浮栅宽度已经降低了20%,你就不会意外地看到明年初他们推出采用对目前50纳米工艺稍加修改的新工艺开发的样片。从更大的角度来说,每次技术迁移都能让我们进一步接近更高性价比的固态驱动器。当我们实现超越时,必将出现新的消费产品,并产生对半导体技术领域更高容量的需求。过去几年中我们在半导体行业获益良多,我非常期待这样的技术进步。

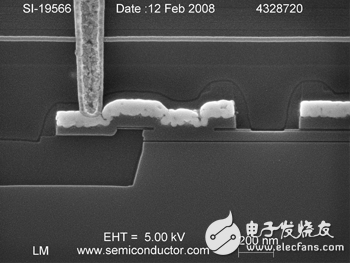

图1:多晶硅电容结构。底部的黑线是低位多晶硅板。

图2:16Gbit闪存的多晶硅电容结构,图中显示了低位板接头。IMFT的4G、16Gbit NAND闪存

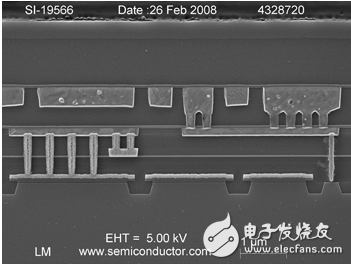

图3:IMFT的16Gbit MLC闪存的金属层2和层3采用铜双镶嵌工艺,金属层1采用钨双镶嵌工艺。

IMFT公司16Gb闪存的多晶硅电容结构不同于早期的50nm 4Gb,它从基于铝的互连技术转向了铜互连技术,并且修改了STI整合的顺序。

- 可应用三维存储结构PCM的高集成NAND型相变内存方案(05-01)

- 简析:固态硬盘(SSD)相关概念(06-11)

- 基于浮栅技术的闪存(09-18)

- 新型混合光驱 (ODD) 的闪存解决方案(10-03)

- 应用于闪存微控制器的“新闪存”架构技术(10-17)

- 四种闪存设计优劣点分析(05-18)