FPGA主要功能模块介绍(1)

时间:02-11

来源:网络整理

点击:

每个模块的功能如下:

1. 可编程输入输出单元(IOB)

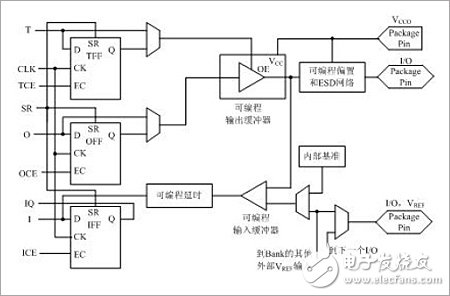

可编程输入/ 输出单元简称I/O 单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/ 输出信号的驱动与匹配要求,其示意结构如图2-4 所示。FPGA 内的I/O 按组分类,每组都能够独立地支持不同的I/O标准。通过软件的灵活配置,可适配不同的电气标准与I/O 物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。目前,I/O 口的频率也越来越高,一些高端的FPGA 通过DDR 寄存器技术可以支持高达2Gbps 的数据速率。

图2-4 IOB内部结构

2.可配置逻辑块(CLB)

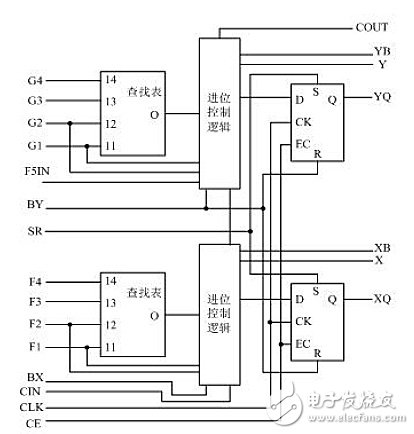

CLB 是FPGA 内的基本逻辑单元。CLB 的实际数量和特性会依器件的不同而不同,但是每个CLB 都包含一个可配置开关矩阵,此矩阵由4 或6 个输入、一些选型电路( 多路复用器等) 和触发器组成。 开关矩阵是高度灵活的,可以对其进行配置以便处理组合逻辑、移位寄存器或RAM。在赛灵思公司公司的FPGA 器件中,CLB 由多个( 一般为4 个或2 个) 相同的Slice 和附加逻辑构成,如图2-5 所示。每个CLB 模块不仅可以用于实现组合逻辑、时序逻辑,还可以配置为分布式RAM 和分布式ROM。

图2-5 典型的CLB结构示意图

图2-6 典型的4输入Slice结构示意图

- Xilinx 7系列FPGA使用之CLB探索(一)(02-10)

- 4G LTE技术很成功,对5G设计有何意义?(05-05)

- 物联网的承诺:下一个重大应用(02-16)

- Xilinx在2017嵌入式世界大会上展示响应最快且可重配置的视觉导向智能系统(02-17)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)

- 基于赛灵思(Xilinx) FPGA的DisplayPort设计与实现(10-23)