FPGA实战开发技巧(12)

时间:02-11

来源:网络整理

点击:

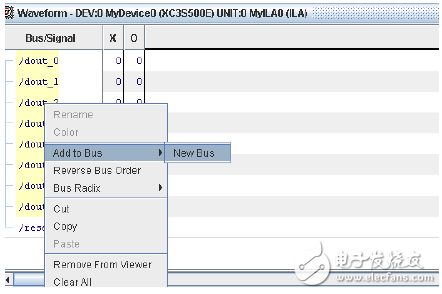

图5-51 添加总线操作示意图

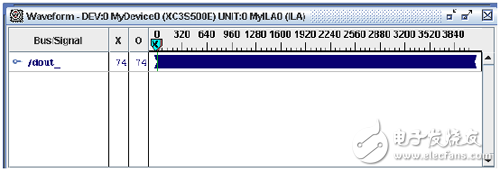

(10) 不设定触发条件采集数据。点击工具栏的" "图标,开始采集数据。整体结果如图5-52 所示,单击工具栏的" "按键,可放大信号,局部结果如图5-53 所示。从分析结果可以看出,本设计在FPGA中成功地完成了8 比特计数器的功能。

图5-52 Analyzer分析结果整体示意图

(11) 设定触发条件采集数据。在"Trigger Setup"栏Match 区域的"M0: Trigger Port0"行的Value 列输入触发条件"0000_0000",如图5-54 所示。

点击工具栏的" "图标,开始采集数据,可以看到,采集结果的第一个数为0,如图5-55 所示。当然,

用户可以根据需要设置更复杂的触发条件。

(12) 利用Bus Plot 功能绘制输出信号波形。在工程区双击"Bus Plot"命令,然后在弹出窗口的"Bus Selection"区域选中"dout",则会将采集数据以图形方式显示出来,如图5-56 所示。由于本设计是8 比特加1 计数器,因此其波形就是幅度为0 到255 的锯齿波。

图5-56 8计数器的波形示意图

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)

- Xilinx全新参考设计提供业界首个单芯片400G解决方案(02-12)

- Xilinx用于工业自动化的机器视觉解决方案(11-30)

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 机器视觉技术原理解析及解决方案集锦(02-06)

- 机器视觉在汽车电子方向的应用解决方案(02-13)