Xilinx可编程逻辑器件设计与开发(基础篇)连载24:Spartan

P总线是否和指定序列匹配,或者是否和指定序列的取反值相匹配。

(5) 上溢和下溢端口逻辑。

DSP48E1 SLICE利用模式检测器检测P[N](N从1到46)是否有溢出,当有上溢或下溢发生时,DSP48E1输出OVERFLOW和UNDERFLOW信号。

三、 算术功能

(1) 预加器。

Virtex-6 FPGA DSP模块结构上的又一改变是在A寄存器路径上增加了一个预加器,实现预加或预减等操作。

(2) 乘法器。

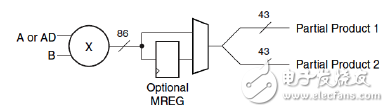

Virtex-6 FPGA DSP模块内包含一个二进制补码乘法器,如图5-23所示。二进制补码乘法器的一个输入为25位的二进制补码,另一个为18位的二进制补码,产生43位结果输出。乘法器86位输出包含两个43位部分乘积。乘法器和算法支持17位操作数右移,以对准宽乘法器的部分乘积(并行或顺序乘法)。级联通路作为Z多路选择器的输入,可以和相邻DSP48E1 SLICE的加法器/减法器相连。

将输入操作数的最高位设置成0,则乘法器就能实现无符号算术。

寄存器MREG是乘法器的输出可选流水线。

图5-23 DSP48E1内的乘法器

(3) 加法器/减法器/逻辑单元。

加法器/减法器/逻辑单元的输出是控制信号和输入数据的函数,加法器/减法器的输入由OPMODE和CARRYINSEL控制。ALUMODE设置加法器/减法器实现的功能。因此OPMODE、ALUMODE和CARRYINSEL信号一起设置加法器/减法器或逻辑单元实现的功能。

(4) 2输入逻辑单元。

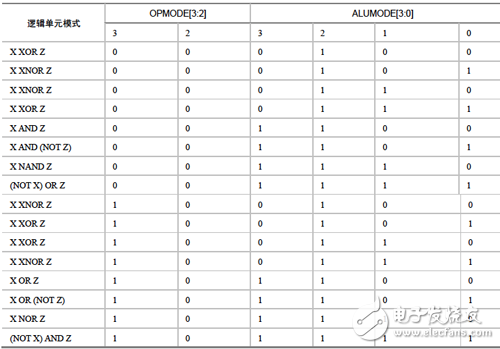

通过OPMODE和ALUMODE的设置,可以在三输入加法/减法/逻辑单元的第二级实现逻辑函数。2输入逻辑单元配置如表5-12所示。

表5-12 2输入逻辑单元配置

分析DSP48E1结构后,可以理解,DSP48E1不需要使用通用可编程逻辑构造资源,可支持将多个DSP48E1逻辑片连接起来完成更宽输入的数字功能、DSP滤波器和复杂算法。这可以带来更低的功耗、更高的性能和更高的芯片资源使用效率。

Xilinx工具提供了便捷的DSP48的使用工具,用户可以在HDL中例化原语,或者调用CoreGen配置所需参数,设置相应功能,工具会自动配置OPMODE及内部寄存器。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)