Xilinx可编程逻辑器件设计与开发(基础篇)连载4:2.1 Spartan

时间:02-11

来源:网络整理

点击:

2.1.1 可配置逻辑模块(CLB)

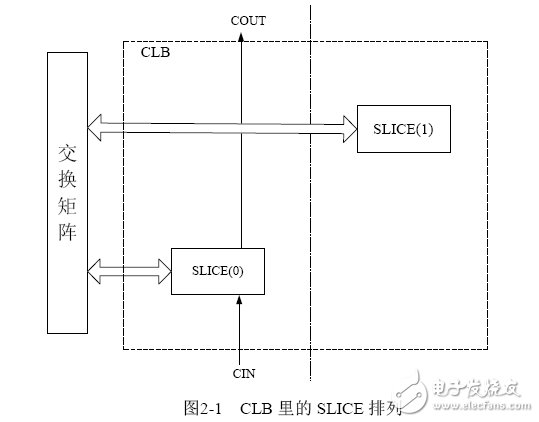

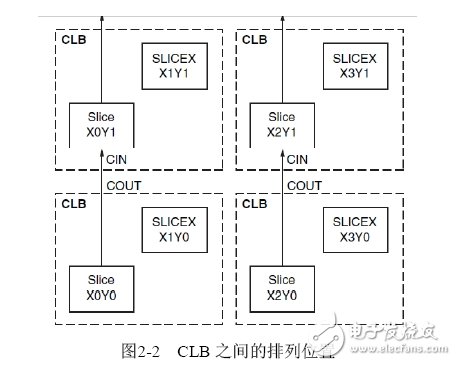

Spartan-6每个CLB模块里包含两个SLICE。CLB通过交换矩阵和外部通用逻辑阵列相连,如图2-1和图2-2所示。底部的SLICE标号为SLICE0,顶部的SLICE标号为SLICE1。两个SLICE没有直接连接。

在Spartan-6中,大约50%的SLICE为SLICEX,它不具有存储功能,也没有进位链;25%为SLICEL,它也不具有存储功能,但包含进位链;剩下的25%为SLICEM,它具有存储/移位寄存器功能,也包含进位链。注意XC6SLX4不含SLICEL。

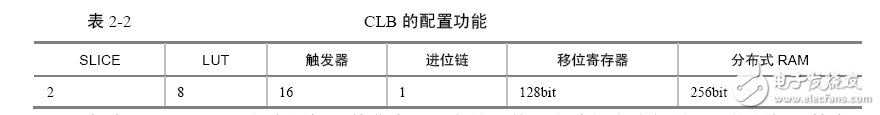

所有CLB的功能是相同的,能够完成表2-2中的配置。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)