Xilinx可编程逻辑器件设计与开发(基础篇)连载22:Spartan

时间:02-11

来源:网络整理

点击:

调节。相移值可在配置过程中固定,也可动态改变。

CLKOUT计数器可分别设置成静态相移模式或者IPFS模式,固定相移模式下,动态相移接口不能被使用。

(3) 动态相移接口。

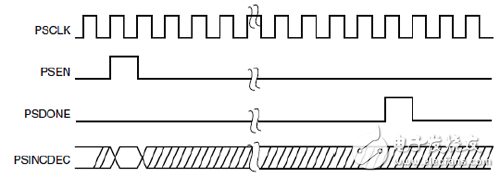

Virtex-6可以由PSEN、PSINCDEC、PSCLK和PSDONE控制动态相移。MMCM锁住后,CLKOUT_PHASE属性决定初始相位,通常情况下,可以不设置初始相移。MMCM根据PSEN、PSINCDEC、PSCLK和PSDONE信号的动作,改变输出相移。步长为VCO时钟周期的1/56。信号时序图请参考图5-14。

图5-14 动态相移接口时序图

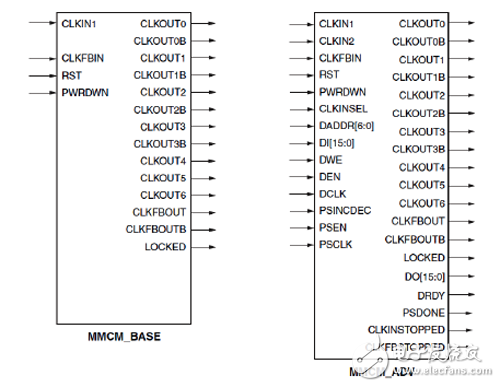

如图5-15所示,MMCM_BASE是基本时钟管理模块的原语,实现MMCM的基本功能;MMCM_ADV是在MMCM_BASE的基础上,增加输入时钟切换、同一CMT中MMCM之间连接、动态相移调节等功能。

图5-15 MMCM的两种原语

注意:Virtex-6不支持动态重配置端口。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)