Xilinx可编程逻辑器件设计与开发(基础篇)连载21:Spartan

钟资源

区域时钟网络是独立于全局时钟网络的。它与全局时钟不同,区域时钟信号BUFR的作用区域最多为三个时钟区域,这些网络对于源同步接口设计尤其有用。

区域时钟控制资源和网络由以下通路和组件构成:

(1) Clock-Capable I/O。

每个时钟区域中有4个Clock-Capable I/O引脚对。每个BANK中有4个专用Clock-Capable I/O位置。当用作时钟输入时,Clock-Capable引脚可以驱动BUFIO和BUFR。

如果用作单端时钟引脚,如"全局时钟缓冲器"中所述,外部单端时钟必须接到引脚对的P端,因为只有这一引脚上存在直接连接。

(2) I/O时钟缓冲器(BUFIO)。

BUFIO是用来驱动I/O列内的专用时钟网络,这个专用的时钟网络独立于全局时钟资源,适合采集源同步数据。BUFIO只能由位于同一时钟区域的Clock-Capable I/O驱动。一个时钟区域有4个BURIO,其中的2个可以驱动相邻区域的I/O时钟网络。BUFIO不能驱动逻辑资源(CLB、BRAM等),因为I/O时钟网络只存在于I/O列中。

可以调用BUFIO的原语来使用它。

(3) 区域时钟缓冲器(BUFR)。

BUFR可以驱动其所在时钟区域中的6个区域时钟网络和相邻区域中的6个时钟网络。与BUFIO不同,BUFR不仅可以驱动其所在时钟区域和相邻时钟区域中的I/O逻辑,还可以驱动CLB、BRAM等。BUFR可由CC引脚、本地时钟、GT以及MMCM高性能时钟驱动。BUFR对于要求跨时钟域或串并转换的源同步应用来说,是理想的选择。

可以通过调用BUFR原语来使用它。

(4) 区域时钟网络。

除了全局时钟树和全局时钟网络,Virtex-6器件还包含区域时钟网络。和全局时钟树一样,这些区域时钟树也是为低歪斜SKEW和低功耗操作设计的。区域时钟网络的传播是仅限于一个时钟区域。一个时钟区域包含6个独立的区域时钟网络。

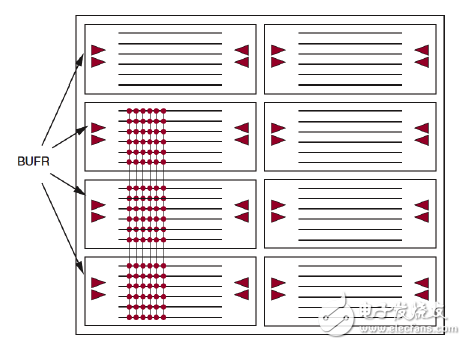

要进入区域时钟网络,必须例化BUFR。一个BUFR最多可以驱动两个相邻时钟区域中的区域时钟,如图5-9所示。此时,BUFR的作用区域为三个时钟区域。顶部和底部区域中BUFR只能连接相邻的一个时钟区域,也就是说,顶部的BUFR连接它所在的下面一个相邻区域。底部的BUFR只能连接它所在的上边一个相邻区域。因此,底部和顶部BUFR的作用区域为两个时钟区域。

图5-9 区域时钟和时钟网络

(5) 水平时钟缓冲器(BUFH)。

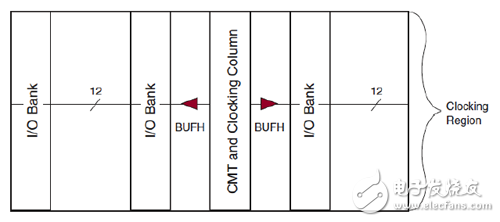

BUFH驱动区域中的水平全局时钟树,如图5-10所示,每个区域有12个BUFH,每个BUFH有一个CE脚,该引脚可控制时钟动态开关。BUFH可由以下几种资源驱动。

同一区域的MMCM输出。

BUFG输出。

局部互联。

同一区域内部inner columns的CC引脚。

图5-10 时钟区域中BUFH位置图

可以通过时钟CE脚关掉时钟来节省功耗。同BUFG驱动两个相邻区域相比,BUFH的功耗更低。

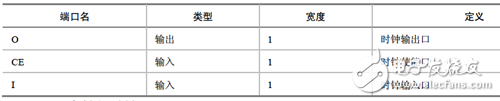

BUFH的原语如表5-9所示。

表5-9 BUFH的原语

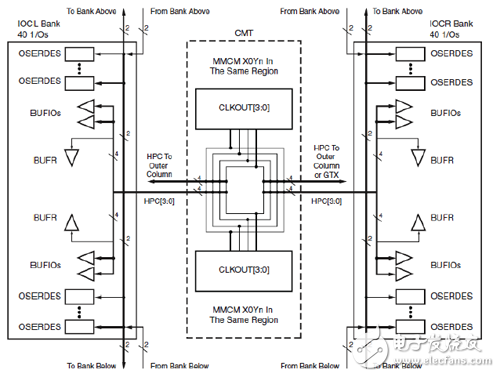

(6) 高性能时钟(HPC-High Performance Clock)。

Virtex-6每个I/O列包含4个HPC。这些时钟由MMCM电源驱动,不由VCCINT供电,因此,这些时钟能改善JITTER和占空比。HPC结构图如图5-11所示,在I/O列中,HPC连接BUFIO,驱动I/O逻辑。4个HPC中的2个可以不通过多区域BUFIO直接驱动I/O BANK(上和下BANK)。HPC可以不通过另一个时钟缓冲器直接连接到OSERDES,提供了一个改善JITTER和占空比性能的时钟。HPC没有专用缓冲器与它相连,ISE软件自动检查设计中IOLOGIC的连接,确定HPC的连接。HPC能驱动同一区域中的BUFR,支持源同步接口设计。

图5-11 HPC结构图

四、 I/O时钟

第三种时钟控制资源是I/O时钟,其速度非常快,可用于局部化的I/O串行器/解串器电路。I/O时钟信号只驱动一个区域。这些I/O时钟网络对于源同步设计尤其有用。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)