Xilinx可编程逻辑器件设计与开发(基础篇)连载36:Spartan

第10章 PlanAhead工具应用

PlanAhead工具是Xilinx提供的一个集成的、可视化的FPGA设计工具,它可以被应用于FPGA设计过程中的不同阶段,常见的应用包括用PlanAhead进行RTL源代码的开发、I/O引脚规划、RTL网表分析、布局布线结果的分析、布局规划,还可以在PlanAhead中将Chipscope核插入设计辅助调试,从而提高性能。也可以用PlanAhead尝试各种实现属性的不同设置,应用不同的时序约束、物理约束和布局规划技术来提高设计性能。我们还可以将ISE的布局布线结果导入PlanAhead进行分析,定位关键路径,找到影响设计性能的真正原因,并通过添加合理的约束、尝试多种布局规划策略以提高设计性能。

PlanAhead具有以下功能。

I/O引脚规划。

RTL开发和分析。

综合和实现。

设计分析。

静态时序预估。

时序约束编辑器。

强大的布局规划。

基于块的逻辑设计。

值得一提的是,PlanAhead已经集成于ISE 11.x中,包括综合前引脚规划——I/O pin planning(Pre-Synthesis)、综合后引脚规划——I/O pin planning(Post-Synthesis)、综合后区域/引脚/逻辑规划——Floorplan Area/IO/Logic(Post-Synthesis)和实现后时序分析/设计规划——Analyze TIming/Floorplan Design(Post-ImplementaTIon),它替代了以前常用的PACE和Floorplanner工具。

10.1 PlanAhead开发流程

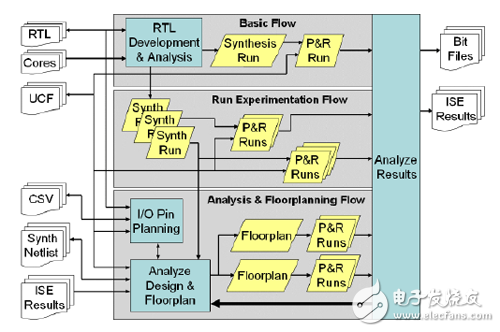

如图10-1所示,PlanAhead设计流程主要包含三个部分,分别是基本设计流程、实验流程和设计分析/布局规划流程。下面分别简单介绍。

基本设计流程(Base Flow):此流程允许设计者导入RTL源文件,再对其进行综合、实现和结果分析。如果希望进行设计分析和布局规划,就要使用设计分析与布局规划流程。

实验流程(Run ExperimentaTIon Flow):设计者可以应用不同的设计策略,使用多种综合、实现属性的组合,尝试进行多个综合或实现过程。PlanAhead工具提供了多种不同的实现策略,它也允许设计者自定义策略。例如,设计者可以在综合阶段指定面积优化、速度优化,或者功耗优化策略,运行多个综合过程,产生不同综合策略下的综合结果,再对其进行分析。设计者也可以在实现阶段,通过设置不同的翻译、映射、布局布线属性,产生多种实现结果。

设计分析与布局规划流程(Analysis & Floorplanning Flow):PlanAhead可以对综合后网表进行分析,对逻辑资源、引脚进行布局规划,还可以将ISE的实现结果导入PlanAhead进行分析和布局规划。

图10-1 PlanAhead设计流程

下面会对各种设计流程做详细的介绍。

10.2 PlanAhead输入、输出文件

PlanAhead的输入文件:

RTL Source File:源文件,包括Verilog/VHDL等。

Xilinx Cores (NGC / NGO):Xilinx核网表文件。

XST Constraint Files (XCF):XST约束文件。

I/O Port Lists (CSV):I/O引脚列表文件,CSV格式。

I/O Port Lists (HDL - Verilog or VHDL):I/O引脚列表文件,HDL格式。

Top-Level Netlists (EDIF):顶层网表,EDIF格式。

Module-Level Netlists (EDIF):模块网表,EDIF格式。

Top-Level Netlists (NGC):顶层网表,NGC格式。

Constraint Files (UCF / NCF):约束文件,UCF/NCF格式。

Xilinx ISE Placement Results (NCD/XDL):Xilinx ISE布局结果,NCD/XDL格式。

Xilinx TRCE TIming Results (TWX/TWR):时序分析报告。

PlanAhead输出报告:

I/O Pin Assignment (CSV):I/O引脚约束文件,CSV格式。

I/O Pin Assignment (RTL - Verilog or VHDL):I/O引脚约束文件,HDL格式。

Log File (planAhead.log):PlanAhead日志文件,包含了运行PlanAhead命令产生的信息内容,可以运行Window→View Log File打开此文件。

Journal File (planAhead.jou):Tcl命令文件。

Error Log Files (planAhead_pidxxxx.debug & hs_err_pidxxxx.log):错误日志文件。

DRC Results (results_x_drc.txt):DRC文本文件。

TimeAhead Results (Excel file):时序规划文件。

Netlist Module, Pblock, and Clock Region Statistics Reports:网表模块、物理块、时钟域统计报告。

SSN Analysis Report:SSN分析报告。

WASSO Analysis Reports:WASSO分析报告。

PlanAhead环境设置信息:

View Display Options File (planAhead.ini &

.patheme):显示PlanAhead初始化文件,PlanAhead工具的显示属性等设置保存在此文件中。

Window Layout

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)