Xilinx可编程逻辑器件设计与开发(基础篇)连载12:Spartan

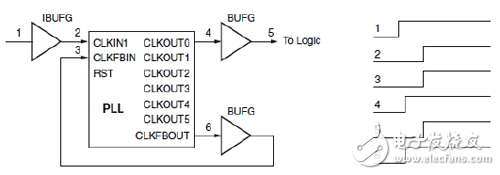

,当需要90°相移时)。右侧所示相关时钟的波形是输入时钟与输出时钟需要相位对齐的情况。这种PLL的配置方式最灵活,但它需要两个全局时钟网络。

图2-24 PLL使用两个BUFG的时钟去歪斜

这里,对反馈时钟有些限制,也就是PFD的2个输入时钟的频率必须完全相同。因此,必须满足下列关系式:

?IN/D=?FB=?VCO/M

例如,如果?IN是166MHz,D=1,M=3,O=1,则VCO的输出时钟频率和PLL的时钟(CLKBOUT)输出的频率都是498MHz。因为反馈通路中的M值是3,所以PFD上的两个输入时钟频率都是166MHz。

另一种更复杂的情况是输入频率为66.66MHz,D=2,M=15,O=2。在这种情况下,VCO的频率是500MHz,而O的输出频率是250MHz。所以,PFD上的反馈频率是500/15,即33.33MHz,与PFD上输入时钟频率的66.66MHz/2相符。

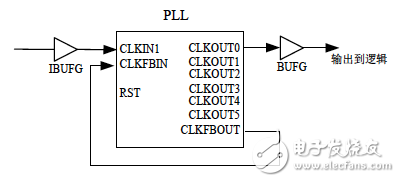

如果PLL用作频率合成器或抖动滤波器,并且PLL输入时钟与PLL输出时钟之间不要求有相位关系,那么PLL反馈可以是PLL的内部反馈。因为反馈时钟根本不通过内核电源供电,所以反馈时钟不受内核电源噪声干扰,因而PLL的性能会有所提升,如图2-25所示。当然,CLKIN信号和BUFG上引入的噪声依然存在。

图2-25 具有内部反馈的PLL

(2) 零延迟缓冲器。

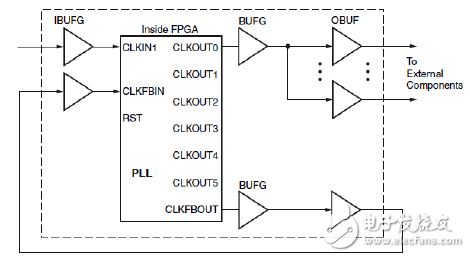

如果系统中只有一个时钟,而这个时钟又需要驱动到所有的器件,为了保证时钟到达各目的器件之间的歪斜尽可能小,该如何实现这个应用呢?这时,就需要用PLL的零延迟缓冲器的应用模式。如图2-26 所示,其中,反馈信号在片外传递,经过了一段PCB板的走线。使用这种配置,可以保证在FPGA的时钟输入引脚和外部器件的时钟输入引脚时钟边沿是对齐的。很显然,在反馈路径中,PCB走线的最大延迟是有限制的。

图2-26 零延迟缓冲器

在某些情况下,由于外部器件输入电容与FPGA反馈路径上的输入电容存在差异,很难实现精准对齐。例如,如果外部器件有1pF~4pF的输入电容,而FPGA 的输入电容是8pF,这样一来,信号斜率就会存在差异,这是基本的时钟歪斜。为了确保时序,设计人员有必要了解这种问题的存在。

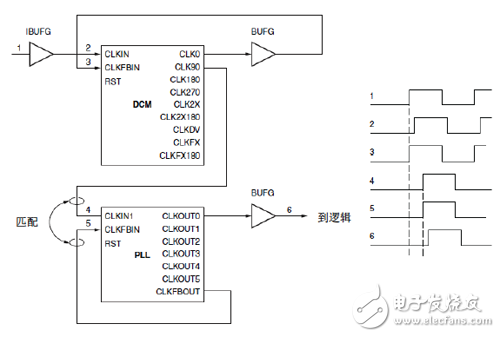

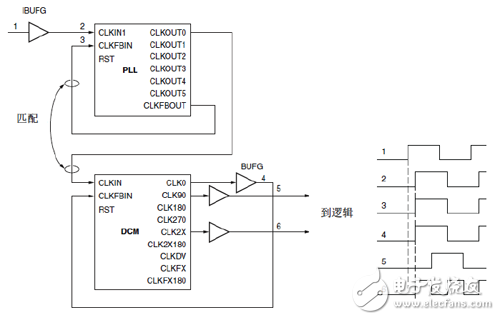

(3) DCM 驱动PLL。

DCM提供了一种生成精确相移时钟的好方法,但是,DCM不能降低参考时钟固有的抖动。PLL可用来降低DCM输出时钟抖动。如图2-27所示,将PLL配置成不引入任何相移(通过PLL的零延迟)的模式,框图右侧所示为相关波形。当使用DCM的输出直接驱动PLL时,DCM和PLL必须同处在一个CMT模块内。这种实现方案在局部专用布线上产生的噪声量最小,因此是首选方案。不过,也可以把DCM输出CLK90连接到BUFG,再去驱动PLL的CLKIN输入。

图2-27 DCM 驱动PLL 以降低抖动

(4) PLL 驱动DCM。

减少时钟抖动的另一种可选方案是在输入时钟抖动传入DCM之前用PLL将其清除。这样可以改善所有DCM的输出抖动,但DCM附加的任何抖动都仍会传到时钟输出。PLL和DCM应处在同一个CMT模块中,因为PLL与DCM之间存在用来支持零延迟模式的专用资源。如果PLL和DCM不在同一个CMT中,那么唯一的连接就是通过一个能抑制歪斜可能性的BUFG。只要参考频率可以由一个PLL生成,则一个PLL即可驱动多个DCM。例如,如果将一个33MHz的参考时钟送入PLL,而设计用一个DCM在200MHz频率下工作,同时用另一个在100MHz频率下工作,那么VCO就可以在600MHz(M1=18)频率下工作。可以对VCO的频率进行三分频以生成200MHz的时钟,同时可以对另一个计数器进

行六分频以生成100MHz的时钟。对于图2-28中的示例,一个PLL可以驱动两个DCM。

图2-28 PLL驱动一个DCM

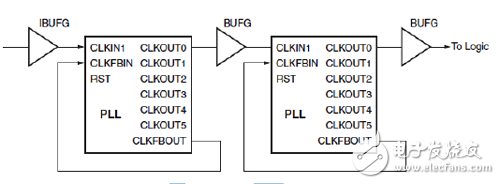

(5) PLL 到PLL 的连接。

可以级联PLL,以便生成更大范围的时钟频率。公式2-1所示为最终输出频率与输入频率之间的关系。图2-29所示为两个PLL的级联,第一个PLL的输出连接到BUFG,再连接到第二个PLL的CLKIN引脚。此路径具有最小的器件抖动。

公式2-1:

图2-29 PLL驱动PLL

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)