Xilinx可编程逻辑器件设计与开发(基础篇)连载28:Spartan

第9章 ChipScope Pro调试设计

在传统的FPGA设计中,调试时大都采用示波器和逻辑分析仪。FPGA和PCB设计人员保留一定数量FPGA引脚作为测试引脚,FPGA设计者在编写FPGA代码时,将需要观察的FPGA内部信号定义为模块的输出,在综合实现时再把这些信号锁定到保留的测试引脚上,最后连接示波器或逻辑分析仪的探头到这些测试脚进行观测。这个测试方法存在很多局限性,成本高、灵活性差、操作麻烦。

成本高。示波器、逻辑分析仪的成本较高。

灵活性差。要测试FPGA的内部节点,需要修改设计,将待测信号引到FPGA引脚上来进行测试。PCB设计完成后这些用作测试引脚的位臵和数量就固定了,不能灵活改变。如果测试引脚不够用时,影响测试。如果测试引脚太多,又将影响PCB布局和布线。而且在一些极端设计中,FPGA的I/O引脚可能已经用光,根本没有多余的引脚被用来做测试引脚。

操作麻烦。示波器、逻辑分析仪必须通过探头连接到测试引脚,容易造成短路,损坏器件。

随着FPGA的规模不断增大,FPGA的设计变得越来越复杂,其封装形式大多向球形方式转移,传统的使用探针监测信号的方式变得越来越困难。Xilinx推出的集成化逻辑分析工具ChipScope Pro,完全解决了这些问题。

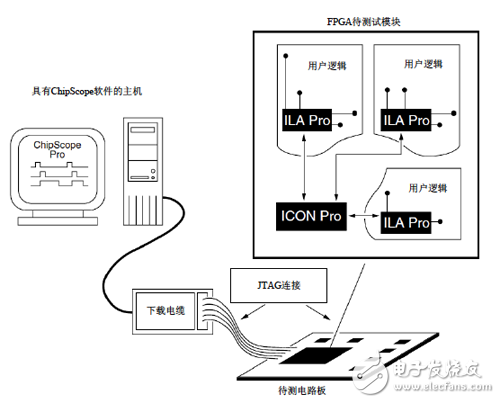

ChipScope Pro具有传统逻辑分析仪的功能,价格便宜,而且不需要附加大量探头,具有很高的实用价值。它是针对Xilinx Virtex系列和Spartan系列器件设计的片内逻辑分析工具,它通过JTAG口,将FPGA内部信号实时读出,传入计算机进行分析。基本方法是利用FPGA内的BRAM,存储信号波形数据,然后通过JTAG接口将数据传送到计算机,并将波形在计算机显示出来。ChipScope测试系统连接结构图如图9-1所示。

使用这种技术观察FPGA内部信号的测试方法,具有以下优点。

成本较低。仅需要ChipScope Pro 设计软件和一根下载电缆,极大地简化了PCB的设计成本。

较高的灵活性。不需将待观察的信号通过额外的引脚输出到FPGA,信号的数量和存储深度由器件BRAM决定。器件中BRAM越多,可观察的信号数量和存储深度就越大。

使用方便。ChipScope Pro在 ISE工具中作为一个IP模块来调用,可以方便地选择待测信号,也可以设臵复杂的触发条件。

图9-1 ChipScope 测试系统连接结构图

ChipScope Pro由一系列相关的IP 核及其软件工具组成,包括核生成器(Core Generator)、核插入器(Core Inserter)、分析仪(ChipScope Analyzer)和TCL 脚本控制接口。

(1) 核生成器

Xilinx Core Generator Tool(Xilinx 核生成器):通过它可以生成集成控制器核(ICON)、集成逻辑分析核(ILA)、虚拟I/O 核(VIO)及安捷伦跟踪核(ATC2)的网表和实例化所需的模板文件。

IBERT Core Generator(IBERT 核生成器):通过它生成Virtex-4 和Virtex-5 系列的误比特率测试核(IBERT)的网表和实例化所需的模板文件。

(2) 核插入器

Core Inserter(核插入器):自动将CON、ILA 和ATC2 核插入已经综合完成的设计中。

PlanAhead Design Analysis Tool(PlanAhead 设计分析工具):自动将ICON 和ILA 核插入设计网表中。请参考PlanAhead 章节内容。

(3) ChipScope Analyzer(ChipScope 分析软件):通过它可以配置FPGA,可以设定触发条件,可以设定ILA、IBA/OPB、IBA/PLB、VIO 及IBERT 的踪迹显示方式。

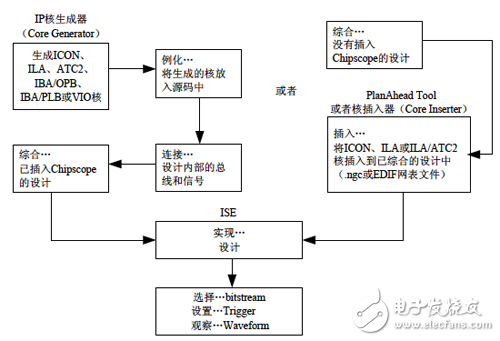

(4) ChipScope Engine Tcl (CSE/Tcl) ScripTIng Interface(TCL 脚本控制接口):通过TCL 脚本语言和JTAG 链,完成与芯片的通信交互。在设计中,使用ChipScope Pro 有两种操作流程,如图9-2 所示。

图9-2 ChipScope 操作流程图

流程1:通过ChipScope Pro 内核生成器,产生各种不同功能调试内核,如ICON、ILA和IBA 等,将生成的例化代码插入HDL 源程序中,再对包括ChipScope Pro 内核的设计进行综合实现后下载到器件中,利用ChipScope Analyzer 进行分析。

流程2:利用ChipScope Pro 的内核插入器将所需要的内核直接插入到已经综合完成的设计网表(NGC 或EDIF)中,然后对这个新的网表文件布局布线后下载到器件中,利用ChipScope Analyzer 进行分析。

接下来我们详细介绍ChipScope 的IP 核及其应用,重点介绍如下内容。

ChipScope Pro 核生成器及各核的属性。

ChipScope 内核插入器。

ChipScope Pro Analyzer 核分析仪。

在FPGA Editor 中修改ChipScope 核信号连接。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)