Xilinx可编程逻辑器件设计与开发(基础篇)连载31:Spartan

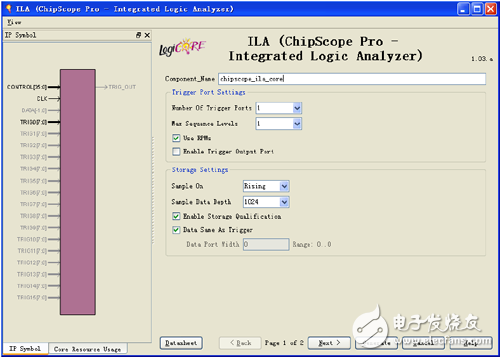

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者创建一个新的IP核工程。【View by funcTIon】→【Debug & VerificaTIon】→【ChipScope Pro】,双击ILA。弹出ILA触发和配置界面,如图9-7所示。

(1) 【Component Name】:输入组件名称。

(2) Trigger Port SetTIngs选项组:触发端口设置。

【Number Of Trigger Ports】:设臵触发端口的个数。每个ILA核最多可以支持16个触发端口。设臵好触发端口的数量后,每个触发端口对应一组选项,包含触发宽度、触发条件等,对应标号为TRIGn,其中n代表触发端口号0到15。

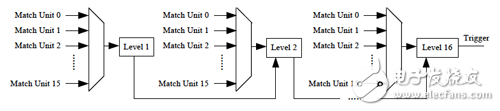

【Max Sequence Levels】:为触发条件设臵最大序列级数。如图9-8 所示,前一级的输出在条件满足的情况下,可以作为下一级的条件,以此类推,可以最大传递16 个状态。

图9-7 ILA 配置界面

图9-8 触发序列器框图

【Use RPMs】:选择是否用相关布局宏(RPM)生成ILA 核,以提高性能。如果选择该选项,则会阻止布局布线器对ILA 核内部进行布局优化,保持其较好的时序特性。通常推荐使用该选项。

【Enable Trigger Output Port】:使能ILA 触发输出端口。在HDL 代码设计中,将该触发端口输出至FPGA 引脚,可以用于触发外部测试设备。该触发输出端口也可以和设计的其他逻辑相连,作为触发、中断或者控制信号。其波形(电平或者脉冲)和极性(高有效或者低有效)可以在运行中通过分析工具随时控制。ILA 触发输出相对于触发输入延时10 个时钟周期。

(3) Storage SetTIngs 选项组:存储选项设置。

【Sample On】:选择上升沿还是下降沿触发。

【Sample Data Depth】:设臵ILA核最大数据采样深度,它与器件BRAM容量有关。

【Enable Storage Qualification】:存储限制条件,它不同于触发条件,但它可以与触发条件配合使用,是Trigger的一种补充。当被测逻辑满足触发条件后,可以通过该选项来控制采样到的数据是否可以被记录到存储器中,默认为使能。所以,触发条件和存储限制条件可以组合在一起,来决定捕获进程什么时候开始,捕获什么样的数据。

【As Trigger】:选择数据和触发条件是否相同。如果选中此功能,数据和触发条件相同,这是大多数逻辑分析中常用的一种模式,因为用户可以捕获和采集任何触发ILA内核的数据。独立的触发端口也可以被排除在数据端口之外,这样的话,数据输入端口将不会出现在ILA核的端口映射中。如果禁止此功能,数据端口将完全独立于触发端口,这种模式限制了被采样数据总量,节省了BRAM资源。如果禁止了此功能,用户将需要设臵【Data Port Width】参数。

【Data Port Width】:ILA采样数据的宽度。如果数据和触发字互相独立,那么允许的最大数据宽度将取决于器件类型和数据深度。Spartan-3、Spartan-3E、Spartan-3A、Spartan-3A DSP和Virtex-4支持的最大数据采样宽度为256 bit,其他器件支持的最大数据宽度为4096bit。

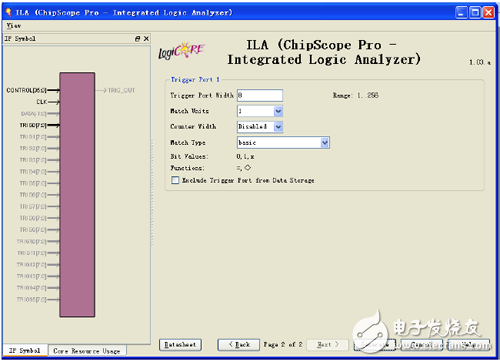

设置好ILA核的触发和存储选项后,单击【Next】。进入ILA触发端口设置界面,如图9-9所示。

图9-9 ILA触发端口设置界面

(4) Trigger Port 1选项组:触发端口1选项组。

【Trigger Port Width】:触发端口宽度,最大为256位。

【Match Units】:设臵触发端口的匹配条件的个数,用于检测触发端口是否满足设定的条件。一个触发器最多可以有16个触发匹配单元。匹配类型在【Match Type】下拉列表框中选择。

【Counter Width】:匹配单元计数器宽度,用于设臵满足匹配条件的次数。最大32位宽。

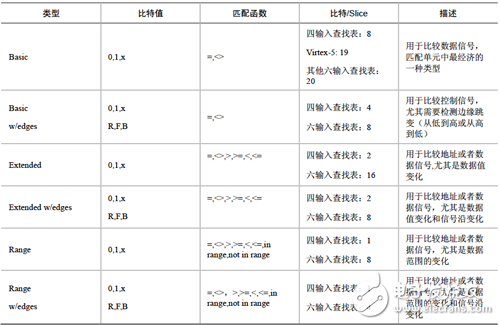

【Match Type】:匹配类型选择,ILA核支持六种匹配类型(Basic、Basic w/edges、Extended、Extended w/edges、Range以及Range w/edges),如表9-1所示。

【Exclude Trigger Port from Data Storage】:是否从所采样和保存的数据中删除触发端口。当选择【Data Same As Trigger】复选框时,该选项有效。

配置完毕后,会在界面右侧的【Core Utilization】栏自动给出核所占用的资源。

表9-1 触发条件判断单元类型列表

说明:

(1) "0"表示"逻辑0","1"表示"逻辑1","X"表示"未知","R"表示"从0到1的跳转","F"表示"从1到0的跳转","B"表示"任何电平跳转"。

(2) 比特/Slice数值只是说明不同匹配单元的大致资源利用率,不能用精确的硬件资源消耗评估。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)