Xilinx可编程逻辑器件设计与开发(基础篇)连载30:Spartan

9.2 ChipScope Pro核生成器

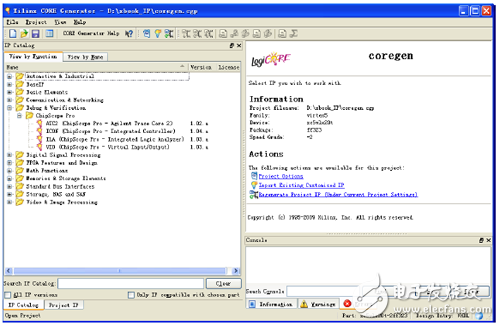

Xilinx针对不同类型的调试IP核,提供了不同的核生成器。本节重点介绍Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro调试IP核ICON、ILA、VIO和ATC2及其属性(见图9-5)。

图9-5 Xilinx Core Generator Tool的调试IP核

9.2.1 ICON属性

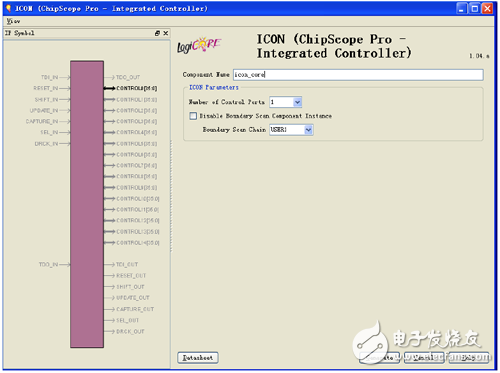

双击【Xilinx Core Generator】,打开现有的IP核工程项目或者建立一个新的IP核工程。【View by funcTIon】→【Debug & VerificaTIon】→【ChipScope Pro】,双击ICON。弹出图9-6所示界面。

图9-6 ICON配置界面

(1) 【Component Name】:输入组件名称。

(2) ICON Parameters。

【Number of Control Ports】:ICON可以连接最多15个ILA、IBA、VIO和ATC2内核。这些内核不可以分享它们的控制端口。

【Disabling the Boundary Scan Component Instance】:该选项用于选择是否禁止在ICON内部例化边界扫描组件,默认此项不选中,即自动在ICON内部例化边界扫描组件。边界扫描原语(例如,BSCAN_VIRTEX5)用于实现与目标FPGA的JTAG边界扫描逻辑的通信。边界扫描组件扩展了FPGA的JTAG测试访问接口(TAP),可以产生四条扫描链,分别是USER1、USER2、USER3和USER4,ChipScope Analyzer是通过其中的一条与ChipScope内核IP通信的。由于这些调试内核不能同时使用一个边界扫描模块中的两条扫描链,但是与其他用户逻辑共享同一个边界扫描模块是可能的。这种共享同一个边界扫描模块的方法有两种:一是在ICON中例化边界扫描模块,并将未用的边界扫描链从ICON输出,供其他逻辑使用;另一种方法是在设计中的其他地方例化边界扫描模块,将USER1或USER2扫描链与ICON核接口连接。

注意:只有 Spartan-3、Spartan-3E、Spartan-3A和Spartan-3A DSP支持该选项。

【SelecTIng the Boundary Scan Chain】:ChipScope Analyzer分析仪通过一条扫描链(USER1、USER2、USER3或者USER4)与ChipScope内核通信。如果边界扫描模块在ICON核内例化,则可以通过【SelecTIng the Boundary Scan Chain】下拉列表框选择一条扫描链。

【Disabling JTAG Clock BUFG Insertion】:如果边界扫描模块在ICON核内例化,那么可以在JTAG时钟链选择禁止插入BUFG。禁止插入BUFG,JTAG时钟则不会使用全局时钟网络,而采用通用布线资源布线。默认值为自动分配一个BUFG。如果要禁止BUFG插入,那么需要在.XCO文件中设臵内核参数"CSET enable_jtag_bufg=false"。该选项在GUI界面中不出现,需要产生该内核后手动编辑.XCO文件。

注意:只有全局资源非常缺少的情况下才考虑把JTAG时钟放到通用布线中。禁止全局时钟缓冲器可能导致时序问题或者不期望的行为(例如在分析工具中出现"Found 0 cores in device"的错误)。

【Enabling Unused Boundary Scan Ports】:如果边界扫描组件是在ICON核里被例化的,那么可以选择【Enabling Unused Boundary Scan Ports】复选框使能边界扫描组件的未用扫描链USER*,供其他逻辑使用。Spartan-3、Spartan-3E、Spartan-3A和Spartan-3A DSP器件的边界扫描原语有两套端口:USER1和USER2。

Virtex-4/5/6和Spartan-6器件的边界扫描原语有四套端口:USER1、USER2、USER3和USER4,但是同一时刻只有一种端口使能。这些端口提供了与TAP控制器的接口。ICON核通常只与一个USER扫描链通信,因此其他不用的端口可以用于其他逻辑。

注意:只有 Spartan-3、Spartan-3E、Spartan-3A和Spartan-3A DSP支持该选项。另外,只有使用这些USER*口时此项才被使能。如果设臵为使能,但是设计中并没有使用这些端口,一些综合工具可能不会产生与ICON之间的正确连接,甚至会在综合或实现阶段产生错误。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)