Xilinx可编程逻辑器件设计与开发(基础篇)连载42:Spartan

九、 分配高速收发器和时钟逻辑

可以将综合后网表文件导入PlanAhead,然后在PlanAhead 中完成关键时钟,以及相关联的I/O 端口的分配。例如: PlanAhead 可以对某些逻辑进行分组,像高速收发器(Gigbit Transceiver,简称GT),以及相关联的I/O 对,再对这些分组进行逻辑位置的规划、端口的分配等操作。

完成分配,PlanAhead 还可以对完成的设计网表进行DRC、WASSO 校验,以防止规划出错。

打开一个基于网表的项目,完成逻辑对象布局及I/O 端口的分配。

1. 在PlanAhead 中运行【File 】→ 【Open Project 】, 打开如下文件

PlanAhead_Tutorial/Projects/project_cpu_netlist/project_cpu_netlist.ppr。

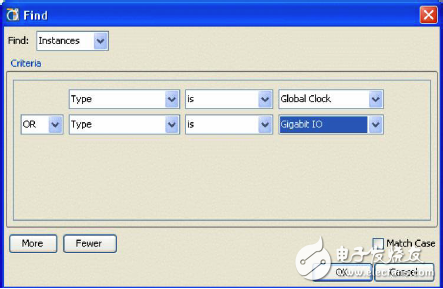

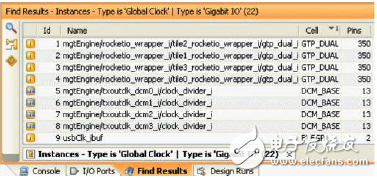

2. 切换到【Floorplan – io_planning_fp】窗口,运行【Edit】→【Find…】,打开图10-54 所示的查找对话框,按图中所示设置,单击【OK】。在查找结果中,单击【Cell】列两次,就会看到图10-55 所示结果,图中显示了项目中用到的时钟以及高速I/O 资源。

图10-54 查找全局时钟及高速I/O

图10-55 查找结果

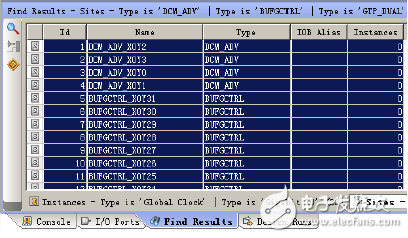

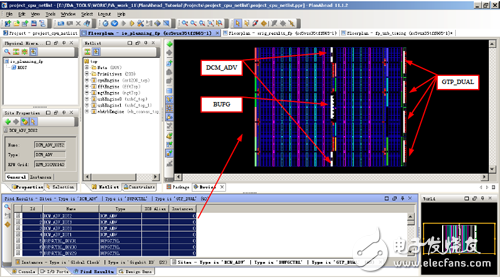

3. 再查找一次,按图10-56 所示设置查找选项,单击【OK】开始查找。图10-57为查找结果,选择所有查找结果,可以在【Device】窗口看到所选元素在器件中的具体位置,如图10-58 所示。

图10-56 查找全局时钟及高速IO

图10-57 查找结果

图10-58 DCM、BUFG、GTP_DUAL 在【Device】中的位置

4. 创建位置约束。

在查找窗口选择Instance 标签,如图10-59 所示。可以看到设计中用到的全局时钟、高速I/O 资源。在【Device】窗口选择按钮,在Device 中创建位置约束。在查找窗口选择第一个GTP_DUAL,按住鼠标左键不放,将其拖放到图10-60 所示的GTP_DUAL 区域,当鼠标由圆形变为加号时,说明找到一个合适的位置,释放左键,这样就完成了一个对象的位置。用同样的方法放置剩余的对象,包括DCM 和BUFG。

需要注意的是,由于DCM 和BUFG 是相互关联的,所以放置DCM 和BUFG 时,相关联的对象要靠近放置。

完成位置约束的【Device】视图

图10-60 完成位置约束的【Device】视图

十、 设计规则DRC 和同步翻转噪声WASSO 检查

在PlanAhead 中可以完成DRC 和WASSO(Weighted Average Simultaneously Switching Noise)的检查。

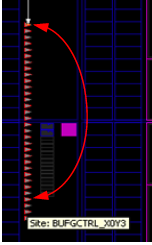

1. 在工具栏单击运行DRC 检查,弹出图10-61 窗口,按照图中所示设置各参数,单击【OK】按钮,开始DRC 检查。检查结果如图10-62 所示,有一个错误,从【ViolaTIon ProperTIes】窗口可以看到,错误的原因是因为DCM 在DCM_ADV_X0Y3 位置,而BUFG 在BUFGCTRL_X0Y5 位置,并提示要纠正此错误,需要将DCM 和BUFG 放置在相同的半边区域内。因为X0Y3 位于器件中部上半部分,所以只需要将BUFG 约束到上半部分就可以了。

图10-61 DRC 检查设置

图10-62 DRC 检查结果

在Virtex-5 器件中,BUFG 分布在器件的中心位置,而且分为上半部分和下半部分。上半部分BUFG 供芯片顶部DCM 用,下半部分BUFG 供芯片底部DCM 用。图10-63 所示为BUFG 修改后的位置。再次运行DRC,会弹出【No violaTIon found】对话框。

图10-63 重新放置BUFG

图10-64 WASSO 分析结果

2. 运行【Tools】→【Run WASSO Analysis】,在弹出的对话框中使用默认值,单击【OK】,开始进行WASSO 分析,分析结果如图10-64 所示。

十一、 导出器件和I/O 引脚配置文件

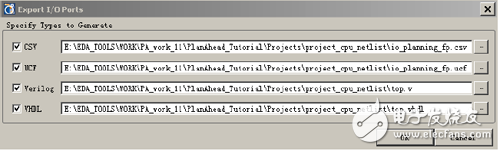

运行【File】→【Export I/O Ports】命令,弹出图10-65 所示对话框,设置要导出的文件。

图10-65 导出器件和I/O 引脚配置文件

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)