Xilinx可编程逻辑器件设计与开发(基础篇)连载29:Spartan

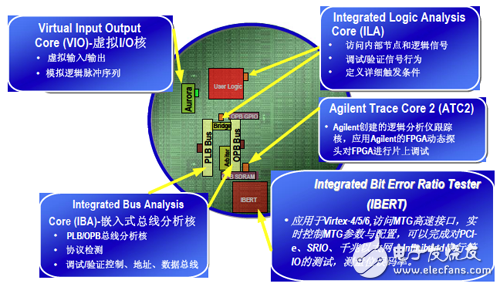

ChipScope Pro 提供了多种不同功能的调试内核,通常分成三类:逻辑调试内核、误比特率测试核和集成总线分析核。用户根据系统的调试要求,应用不同的调试内核,方便快速地找到设计中存在的问题。常用IP 核如图9-3 所示。

(1) 逻辑调试内核。

ICON(集成控制器核)。

ILA(集成逻辑分析核)。

VIO(虚拟I/O 核)。

ATC2(安捷伦跟踪核)。

(2) IBERT(误比特率测试核)。

Virtex-4 FX 平台的IBERT(误比特率测试核)。

Virtex-5 LXT/SXT/FXT 平台的IBERT(误比特率测试核)。

Virtex-6 LXT/SXT 平台的IBERT(误比特率测试核)。

Spratn-6 LXT 平台的IBERT(误比特率测试核)。

(3) IBA(Integrated Bus Analyzer,集成总线分析核)。

IBA/OPB(集成总线/处理器外设总线核)。

IBA/PLB(集成总线/处理器本地总线核)。

图9-3 常用ChipScope 的IP 核

一、 ICON 核

ICON 核具备与JTAG 边界扫描端口通信的能力,因此ICON 核是ChipScope Pro 应用必不可少的关键核。一个ICON 核可以最多同时连接15 个ILA、IBA/OPB、IBA/PLB、VIO或者ATC2 核。在Virtex-4/5/6 和Spartan-6 芯片中,可以通过BSCAN_VIRTEX 原语来使用USER1、USER2、USER3 或者USER4 扫描链,且由于BSCAN_VIRTEX 原语实现了一条单独的扫描链,因此就没有必要导出未使用的用户扫描链。在其余类型芯片中,只能使用USER1 或者USER2 扫描链。

二、 ILA 核

ILA 核提供触发和跟踪功能,根据用户设置的触发条件捕获数据,然后在ICON 的控制下,通过边界扫描端口将数据上传到PC,最后在分析仪(Alalyzer)中显示出信号波形。由于ILA 核和被监控的逻辑是同步的,因此设计中的所有时钟约束会被应用到ILA 核。ILA包括下面3 个主要组件:

输入、输出触发逻辑:输入触发逻辑用于检测各种触发条件;输出触发逻辑用于触发外部测试设备以及其他逻辑。

数据捕获逻辑:数据捕获逻辑用于捕获数据,并将所捕获的数据存储到芯片的BRAM 中。

控制和状态逻辑:控制和状态逻辑用于管理ILA 的各种操作。

三、 VIO 核

VIO(Virtual I/O)核是一个虚拟控制台,用于实时监控和控制FPGA 内部逻辑信号,可以观测FPGA 设计中任意模块的输出信号,也可以对这些模块添加虚拟输入,类似DIP开关、按键等,且不占用BRAM 资源。VIO 核面向模块操作,支持下面4 类信号:

异步输入信号:异步输入信号,由JTAG 时钟信号(TCK)钟控,周期地读入PC,结果显示在ChipScope Pro 分析仪的用户界面。

同步输入信号:同步输入信号,由设计中的时钟钟控,周期地读入PC,结果显示在ChipScope Pro 分析仪的用户界面。

异步输出信号 :异步输出信号,由用户在ChipScope Pro 分析仪中定义,送至周围的逻辑,输出信号的逻辑"1/0"由用户定义。

同步输出信号:同步输出信号,由用户定义,与系统时钟同步,输出信号的逻辑"1/0"由用户定义。

四、 ATC2 核

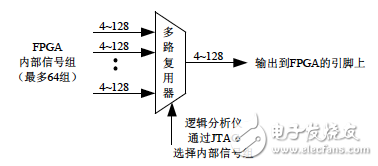

ATC2 核由Xilinx 和Aglient 合作开发,配合Aglient 的最新一代的逻辑分析仪使用。ATC2 内核结构框图如图9-4 所示,可以看成一个可配置的多路复用器,输入为一些信号组,最大可以配置成64 个组。

图9-4 ATC2 结构图

Agilent 逻辑分析仪上运行一个FPGA 动态探测器的应用软件,用它可以观察从FPGA 输出的信号。

ATC2 实现了FPGA 与Aglient 逻辑分析仪的联合调试、捕获数据,允许Aglient 逻辑分析仪访问FPGA 内部任何节点,提供更深的捕获深度,具有更复杂的触发设置,并且支持网络远程调试,功能十分强大。与单独使用ChipScope Pro 相比,减少了BRAM 的使用。

ATC2 与Anlient 逻辑分析仪连接,可以为每个信号提供2M 的捕获深度,是ILA 的60倍。此外,最多允许在FPGA 内部添加64 个观测信号组,和逻辑分析仪的连接路径最多可达128 条。这非常有利于查找设计缺陷。

五、 IBERT 核

IBERT 核用于测量高速串行收发器多条通道上的误码率和实时调整高速串行收发器参数。BERT 核由三部分组成。

BERT 逻辑:BERT 逻辑例化RockeTIO 收发器模块,包含了模式产生器和检测器。有多种模式可以选择,包括简单的时钟模式、完全伪随机二进制序列(PRBS)模式和帧计数模式。

动态重配臵端口(DRP):每个Rocket I/O 收发器都有一个动态重配臵端口,因此,可以动态改变收发器属性。

控制和状态逻辑:管理IBERT 核。

六、 IBA/OPB核

在Xilinx的FPGA中可以嵌入软核处理器MicroBlaze,在一些高端器件中还有IBM的硬核处理器核PowerPC,IBA/OPB核是

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)