Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 24

了解Zynq PS / PL接口之后;到目前为止,我们已经分析了Zynq All Programmable SoC芯片中的PS (处理器系统)与PL(可编程逻辑)之间的接口。我们已经使用Vivado设计套件创建了简单的外设,使用SDK与新外设连接,并且可以在外设上运行自检程序。但我们创建的外设功能不超过四个可读取和写入的寄存器。实际上,我们需要外设执行一些有效的功能。

我们将再次使用Vivado为这个外设添加实际的功能。

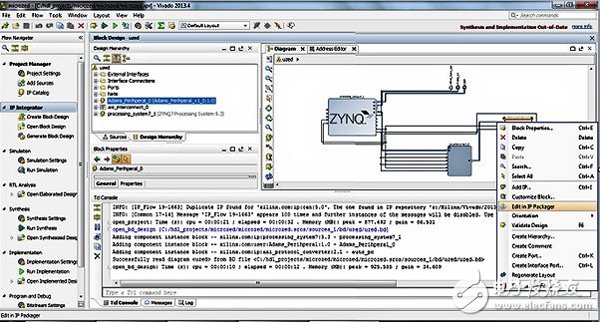

首先需要打开Vivado项目和框图,其中包含我们已创建的外设。右键点击"Peripheral",选择"Edit IP Packager "选项。随后IP Packager窗口将打开,可编辑和更新外设。

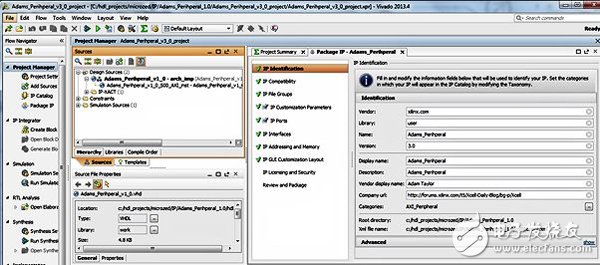

除Package IP 外设窗口外,这个窗口与标准项目流窗口相似。在设计源窗口下方有两个在外设创建过程中创建的文件。

这些文件被命名为:

Adams_Peripheral_v1_0.vhd - 顶级架构文件,利用该文件可定义退出该模块的用户I/O。

Adams_Peripheral_V1_0_S00_AXI.vhd - RTL文件,其中包含函数AXI接口,包括初始创建的四个寄存器。

这两个文件中包括用户代码将插入地址的注解:

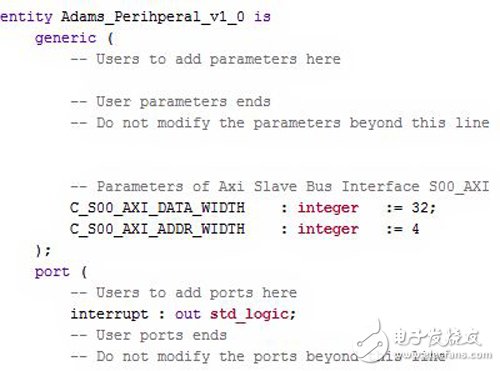

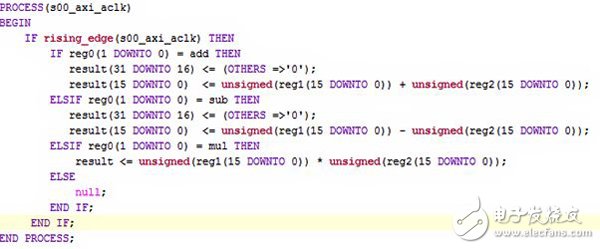

在这个例子中,我将介绍使用第一个寄存器作为控制寄存器。这个寄存器当中的特定位定义是否将寄存器2和3的目录进行相加、相减或相乘运算。运算结果将存储在第四个寄存器中。我们将设置与微处理器相关的第四个寄存器为只读状态,以确保微处理器不会影响运算结果。此外,如果激活控制寄存器,外围将生成一个中断。

定义中的第一步是声明四个寄存器,第3个寄存器为输出寄存器,最后1个寄存器为输入寄存器。(在这个步骤时我们可实现这一功能,但目前我正在顶层操作演示实现更复杂功能所需要的步骤) 。

同时,我也编辑这个文件为只读文件,以防止处理器写入第四个寄存器。

在顶层文件我在该架构创建一个中断输出并添加简单功能代码以执行我们所要的操作。

在所有必要的用户VHDL语言完成添加后,我处理该项目以确保在Vivado内打包IP并返回至项目前不会出现错误。但在打包器打包IP前,我增加IP版本号以表示代码变更。点击"re-package"将运行打包器,并关闭项目,返回至初始Vivado项目。

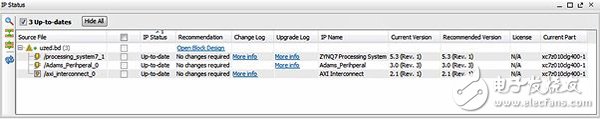

返回使用该外设的项目中,可以运行IP状态报告(Tools - >Reports - >Report IP status),显示在设计中所使用的更新版本。

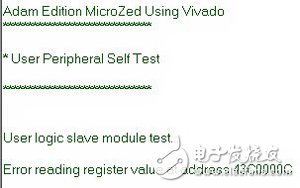

在将项目导出至SDK前,需要重新构建项目。在SDK内,可使用之前使用的同一功能对这个外设进行写入和读取。但测试过程中最后一个寄存器不能写入时,自检程序将失败。

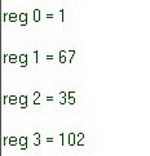

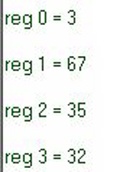

第一个测试是使用寄存器0中的命令1相加寄存器2和3内的目录:

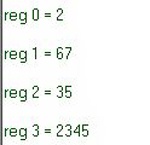

在第二次测试中,我们使用寄存器0中的命令2将寄存器2和3内的目录相乘:

在最后的测试中,我们使用寄存器0中的命令3将寄存器2内的目录减去寄存器3的目录:

所有这些测试都使用轮询的方法。由于这些运算属于简单的加、减、乘函数,可在一个时钟周期内完成。但更复杂的多周期函数运算需要使用中断,我们将在另外的文章中说明。

Zynq 相关文章:

- Xilinx多协议机器视觉摄像机参考设计(12-01)

- 人工智能实现的流派 FPGA vs. ASIC看好谁?(08-27)

- 采用Xilinx Zynq SoC实现眼动追踪技术 让眼睛也可以控制计算机(06-28)

- EyeTech视线跟踪技术如何成为主流?(06-28)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)

- 玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯(11-05)