PIC18F2455/2550/4455/4550之通用串行总线USB

写。 同样,接收缓冲器(OUT端点)和正在使用的 BD单元重叠也将导致不可预料的结果。 在开发USB应用程序时,用户需要考虑在软件中对地址进行验证。

乒乓缓冲:当端点有两组BD项时(一组用于偶数数据传输,一组用于奇数数据传输),它被定义为具有乒乓缓冲器。 这样就允许在CPU处理一组BD的同时,SIE 处理另一组BD。这种方式的乒乓缓冲BD,可实现单片机与 USB之间的最大数据吞吐量。

USB模块支持三种模式的操作:

• 不支持乒乓缓冲

• 仅支持OUT端点0 的乒乓缓冲

• 支持所有端点的乒乓缓冲

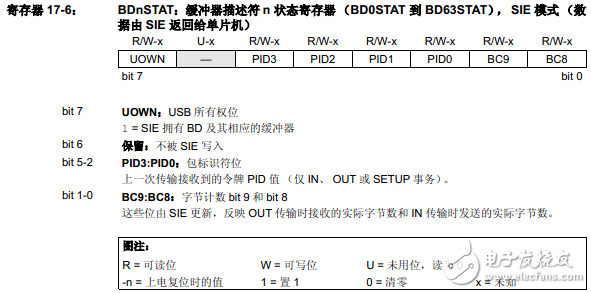

使用UCFG 寄存器中的PPB1:PPB0位设置乒乓缓冲器。USB模块跟踪每个端点的乒乓指针。 当使能此模块时,所有指针都复位到指向偶数BD。 在事务完成之后(UOWN被SIE 清零),指针被切换到奇数BD。在下一次事务完成之后,指针又被切换回偶数BD上次事务的奇偶状态保存在USTAT寄存器的PPBI 位中。 用户可以使用PPBRST 位将所有乒乓指针复位到偶数状态。图17-7 显示了三种不同的操作模式以及BD是如何填充USB RAM 的。根据缓冲配置,BD与特定的端点具有固定的对应关系。表17-4 所示为BD与端点之间映射的详细情况。 这种关系也意味着如果没有连续使能端点,BDT 中将出现空白区域。 理论上被禁止的端点的BD可用作缓冲空间。 实际上,用户应该避免使用BDT 中的这些空间,除非已经采取了验证BD地址的措施。

USB 中断:USB模块可以产生多个中断条件。 要识别所有中断源,和单片机一样,此模块具有自己的中断逻辑结构。

USB 电源模式:最常见的电源模式有仅总线供电(Bus Power Only)、仅自供电(Self-Power Only)和以自供电为主的双电源(Dual Power)供电模式。

并行通信端口:并行通信端口(SPP)是除 USB RAM 之外用于数据传输的备用通道。 可以将端点配置为使用SPP将数据直接发送到外部硬件或直接接收来自外部硬件的数据。

此方法可以把单片机作为数据管理器,直接通过SPP传递大块的数据而无需单片机进行处理。 应用示例将包含数据采集系统,其中外部FIFO的数据通过USB和主机

进行通信。 在这种情况下,单片机控制端点,而原始数据的传送则靠外设完成。通过相关的端点缓冲器描述符将SPP 使能为USB端点的端口。 必须通过以下方法来使能端点:

1. 将BDnADRL:BDnADRH 设置为指向FFFFh 。

2. 将KEN位(BDnSTAT《5》)置 1 以便让SIE 保持对缓冲器的控制。

3. 将INCDIS 位(BDnSTAT《4》)置 1 以禁止地址自动递增。

振荡器:USB模块有特定的时钟要求。 在全速模式下,其时钟源必须为48 MHz。 即便如此,并不要求单片机内核和其他外设以此时钟速度运行或使用同一个时钟源。

USB 固件和驱动程序:Microchip 提供了一些针对应用的特定的资源,比如USB固件和驱动程序。

- 基于PIC微控制器的LED驱动控制电路设计(06-24)

- EMI滤波器的PSpice辅助设计(11-07)

- 超声波测距系统中单片机的应用(10-07)

- 基于音频信号的WSN节点间距测量设计(10-09)

- 浅谈如何借用SEPIC电路拓扑改善LED系统性能(02-06)

- 通过两个PIC引脚驱动六只LED灯(08-02)