典型的嵌入式系统设计

系统中采用了Vxworks实时操作系统,VxWorks 是风河公司(Windriver)开发的实时操作系统之一,以其优秀的可靠性、实时性及内核的可裁减性,被广泛应用于通信、军事、航天、航空、工业控制等关键行业领域,其开发环境为Tornado。

2、处理器的选择:

在为嵌入式系统选择处理器时需要考虑以下几个方面:

性能:处理器必须有足够的性能执行任务和支持产品生命周期。

工具支持:支持软件创建、调试、系统集成、代码调整和优化工具对整体项目成功与否非常关键。

操作系统支持:嵌入式系统应用需要使用有帮助的抽象来减少其复杂性。

开发人员过去的处理器经验:拥有处理器或处理器系列产品的开发经验可以减少可观的学习新处理器、工具和技术的时间。

成本,功耗,产品上市时间,技术支持等等

在本系统的设计中,综合以上各方面的因素,考虑到处理器性能,操作系统支持以及列车上严酷的工业环境等等,在MVB系统中选用了ATMEL用于工业控制领域的工业级的AT91系列ARM处理器AT91M40800,它是基于ARM7TDMI内核,内含高性能的32位RISC处理器、16位高集成度指令集、8KB片上SRAM、可编程外部总线接口(EBI)、3通道16位计数器/定时器、32个可编程I/O口、中断控制器、2个USART、可编程看门狗定时器、主时钟电路和 DRAM时序控制电路,并配有高级节能电路;同时,可支持JTAG调试,主频可达到40MHz。

3、相关外部设备的选择:

在确定操作系统和处理器之后,就可以确定相关的外部设备,如FLASH,RAM,串口等等。在MVB系统中,MVB控制器MVBC(MulTIfuncTIon Vehicle Bus Controller)是一个MVB电路和实际的物理设备之间的接口控制器,它的主要功能是实现MVB总线信号与数据帧的编解码,纠错等功能,是本系统中要实现的关键的硬件模块。由于系统规模,上市时间等方面的要求,系统暂时不考虑ASIC实现,因此在MVB系统中用FPGA来实现这个关键模块,FPGA 是ASIC最灵活和最合算的替代方案。考虑到系统需求与FPGA资源,成本,供货情况等因素,最终选择了Altera公司的Cyclone系列FPGA, 其开发工具是Quartus II。

4、MVB系统架构

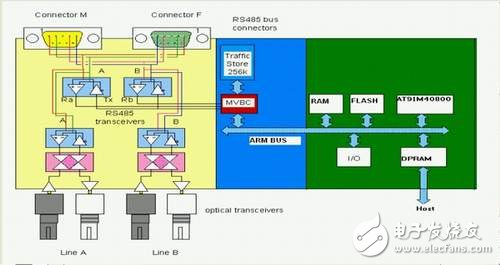

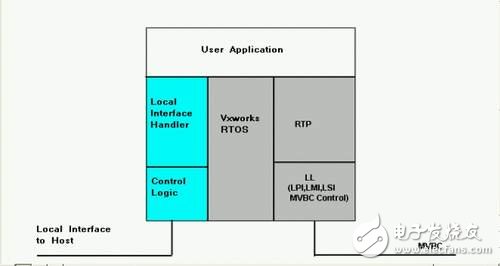

由以上的需求分析和选型,完整的系统硬件架构和软件架构如图2图3所示

图2:MVB系统的硬件架构。

图3:MVB系统的软件架构。

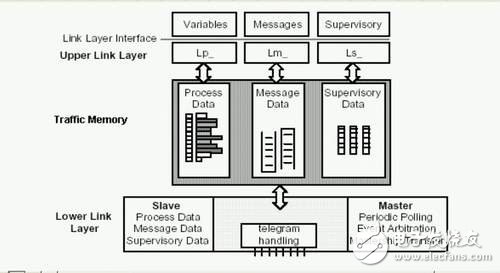

其中,处理器和 MVBC通过Traffic Memory(TM)进行通讯数据交换,所有软件和MVBC要交换的控制信息和数据都可以在TM地址空间中找到,这个地址空间对处理器和MVBC都是可访问的。其示意图4如下

图4:Traffic Memory。

三、步骤3:详细的软硬件设计和RTL代码、软件代码开发

在系统架构确定的基础上,详细的软硬件设计就可以开始了。

1、硬件设计

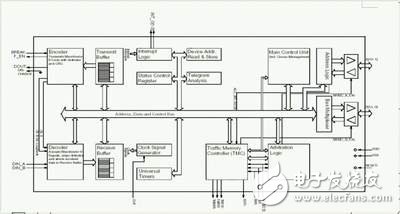

硬件设计设计包括了MVB控制器的FPGA设计和MVB总线系统的板级设计,其中关键的MVB控制器的设计如图5

图5:MVB控制器的框图。(点击放大该图)

如图所示,MVB控制器包含以下功能模块:

编码器:产生曼彻斯特编码,传送数据帧

发送缓冲区:作为要发送的数据和CRC检测值的缓冲区

译码器:接收、曼彻斯特译码,数据提取、数据错误检测

接收缓冲区:作为接收端数据和CRC结果的缓冲区

报文分析单元:检测主帧和从帧超时,帧误检测、错误状态报告

状态控制寄存器:MVBC配置

主控单元:支持MVBC作为主设备或者从设备工作,支持队列消息传送

设备地址读取和储存单元:硬件定义的设备地址可以被不同的值覆盖

地址逻辑:把CPU对MVBC内部寄存器进行访问的输入地址进行解析;产生MVBC访问TM的输出地址

总线复用、转换单元:处理MVBC内部的数据传送

中断逻辑:支持16种中断源;

通用定时器:两个定时输出信号,可提供给系统同步使用

时钟产生电路:产生所有MVBC工作的时钟和计数器

2、软件设计

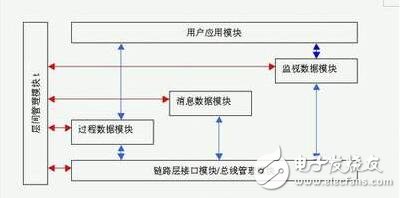

由于在MVB系统中,过程数据,消息数据,监视数据是三种不同的通讯机制,因此,MVB系统软件的模块设计如图6。

四、软硬件的联调和集成

下面,以一个简单的例子来说明MVB系统的软硬件的集成和验证。

过程数据在MVB系统中是周期性发送的数据,其在本系统中的通讯机制如下:对于发送方,用户应用模块将一个端口的过程变量发送给过程数据处理模块,过程数据处理模块按照逻辑端口的设置定时通过链路层接口模块更新Traffic Memory当中的相应逻辑端口的数据,此时发送方软件的任务完成。发送方的MVBC硬件接收总线管理器BA定时发出的主帧,通过译码器解码得到相应的逻辑端口的值,通过查询Traffic Memory相关的逻辑端口发送设置后将MVBC自动

- 嵌入式系统在电源设计中的运用(09-20)

- 基于4G通信的嵌入式数据通信系统设计(10-10)

- 汽车安全性能亟待升级 嵌入式系统把关护航(05-07)

- USB端口找到新居,落户嵌入式系统(02-11)

- 嵌入式系统在电力变压器监测中的应用研究(09-18)

- 基于OMAP架构的嵌入式指纹识别系统设计与应用(04-29)