通过FPGA智能调试工具缩短验证时间

时间:10-10

来源:网络整理

点击:

。

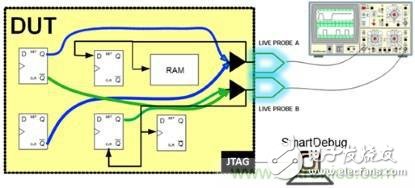

探头插入:这用于在设计中插入其它探头,将信号输出到FPGA封装引脚,以对设计进行评估和调试。这种特点确实需要增加布局布线,从而在I/O增加信号,但并不一定需要完整的重新编译。

图1 现场探头使用实例(来源:美高森美)

FPGA设计人员把30%或更多的时间通常花在调试上。根据项目的规模和状态,甚至需要更多的调试时间。由于调试涉及许多迭代周期,可观察性和可控性有限,经常要重新运行布局布线,时序收敛和重新编程,因此调试是非常痛苦的工作。与仅使用传统插入逻辑分析仪相比,智能调试工具使得工程师能够更快地对他们的FPGA设计进行验证。这些工具使得设计人员在整个设计中可以实时观察信号和控制信号状态,显着提高了调试速度。

最近,据一名客户报告,他们采用内部逻辑分析仪花了一周时间来试图调试一个问题。但在采用智能调试工具代替后,工程师仅仅在两个小时内就找出了问题。最终追踪到,这个问题来自与工程师采用逻辑分析仪时观察的一个完全不同的设计模块。然后工程师利用有源探头特点强制赋予不同的数值,确保电路适当响应的方式,进一步改善了设计。

对FPGA设计人员来说,增强调试能力是影响重大。最新的解决方案能够显著缩短调试验证时间,为FPGA提供无与伦比的可观察性和可控性。结果使得,在选择器件时更重视FPGA调试能力的设计人员,可以缩短开发周期,降低成本,同时显著加快上市速度。

- 逻辑分析仪硬件电路毛刺信号分析(04-02)

- 如何更好地设计面向在板烧录的产品-单线串口篇(05-11)

- 详析数字I/O和逻辑分析仪常用术语(02-18)

- 频谱分析仪六大常见问题解答(02-20)

- 容易被忽略的逻辑分析仪探头(03-28)

- VGA的驱动显示以及逻辑分析仪的使用(02-06)