深入读懂半导体存储技术及市场,鄙文即可!

新主要有两种手段,一是结构上由2D变为3D,二是采用新的存储器件结构或材料,本节我们将从器件结构,功能特性,研发进展等角度对目前最主要的新型存储器进行对比分析。3D XPoint技术是最具革命性的热点技术,故将放在下一节单独重点分析。

1)3D NAND

目前,NAND 闪存的主流制程为28nm/16nm,在制程进入1x nm 世代后,越来越紧邻的存储单元之间的串扰效应,越来越薄的栅氧化层导致的电子击穿效应,都使得NAND的可靠性和性能受到影响。此外,在进入2x nm后,由于平面微缩工艺的难度越来越大,故微缩带来的成本优势开始减弱,尤其是在16nm制程后,继续采用2D 微缩工艺的难度和成本已经超过硅通孔,薄膜刻蚀等3D技术。

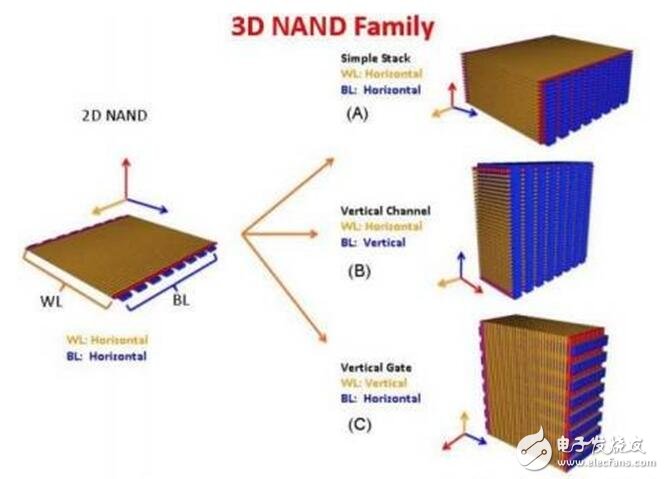

图14, 2D NAND 与 3D NAND的对比

也就是说,不论是从性能角度考虑,还是从经济角度考虑,继续平面微缩都不是一个好办法,因此三星,海力士,东芝,美光等NAND龙头企业都在积极研发3D NAND技术。IC Insight预计,得益于SSD和智能手机的推动,2015年开始3D NAND的出货量将以200%的年均复合增长率递增(2D则以每年17.1%的速度下降),预计2020年达到NAND总量的70%的水平。

3D NAND 优点:

1) 轻松在宽松的制程下得到大容量:从2D NAND到3D NAND就像平房到高楼大厦,因此单位面积的容量更高,目前32层的3D NAND容量为128Gb,与主流2D 1y/1znm NAND的容量持平,而48层的3D NAND存储器容量能够达到256Gb,即层数达到48层后,3D的威力将初步显现,三星预计100层的3D NAND容量将达1TB。

2) 性能更高,功耗更低:得益于立体堆叠的模式,3D NAND能在较大的存储单元尺寸下保持很高的存储密度,大的存储单元接受电荷信号更饱满,栅氧的厚度也更大,不易被击穿,此外,更大容量NAND读写不需要那么多次的重试,因此总功耗也会更低。

主流技术对比:

由于2D NAND的架构关键在于光刻,而3D的关键则在于高深宽比通孔刻蚀,薄膜加工等技术,工艺差别较大,故各家的进展并非一帆风顺。目前3D NAND的研发总体可以分为三大阵营,分别是三星,海力士,东芝,三家都有其相似的技术和专用技术。相同之处在于三者都使用了环栅技术(GAA: gate-all-around),使得栅极对导电沟道的控制能力更强,关断电流也更小。不同之处主要有三点:

三星和海力士在其3D NAND产品中引入了电荷撷取层(CTL:Charge Trap Layer),即将电荷存储在高K(介电常数)材料绝缘层(SiN),而传统的2D NAND则是将电荷储存在导电的多晶硅浮栅上,氮化硅因为结构特殊,电荷往往会自动积聚到它的晶格周围,因此理论上这些电荷不会消耗,从而其寿命可以得到提升。而Intel/美光方面则是仍然采用传统的浮栅极,理由是这项技术在2D NAND中已经久经考验,比较成熟。

东芝/闪迪,西部数据在3D NAND方面是合作关系(西部数据2016年收购了闪迪),均使用一项名叫BiCS(Bit Cost Scaling:位成本可扩展技术)的技术,其3D堆栈上所有存储器单元可以采用相同的晶圆沉积步骤同时生产出来,而且堆叠的存储器单元每个位行只需要一个位线,故可以随NAND规模的扩大而降低成本,号称在所有3D NAND闪存中核心面积最低,成本最低。2015年,东芝/闪迪推出了48层第二代3D NAND Flash(即BiCS2),该产品在一个2bit/cell (16GB)的芯片中堆叠了48个字线层,容量为16GB,其采用的"U"型NAND串结构可以提高阵列密度。

东芝和海力士使用自对准多晶硅栅,而三星则是通过大马士革工艺淀积金属栅。

2)3D DRAM

与NAND Flash技术类似,DRAM的平面微缩也正在一步步接近极限并向垂直方向扩展:18/16nm之后,由于薄膜厚度无法继续缩减,以及不适合采用高介电常数(High-K)材料和电极等原因,继续在二维方向缩减尺寸已不再具备成本和性能方面的优势。与DRAM的3D技术路线不同的是,DRAM的3D技术体现在芯片层面,而非晶体管层面,即其3D指的是3D封装——采用TSV将多片芯片堆叠在一起,随着电子产品对DRAM容量要求和性能的提升,未来3D DRAM比重将呈上升趋势。

3D DRAM优点:

a)宽松尺寸下实现高密度容量:和3DNAND类似,Z方向的扩展能力使得其对平面微缩的要求降低,从而可以在较大制程下大幅提升单根内存条容量。

b)寄生阻容减少,延时串扰降低:改用3D封装之后,很多芯片之间的连接由水平面上交杂的铜线变成了垂直方向的通孔,互连线长度大大降低,从而极大的改善了后道线间延时和串扰,对芯片性能的提升有很大的帮助。

3) PCRAM(相变存储器)

PCM(Phase Change RAM):相变随

- 面对挑战,东芝聚焦这四大热门领域(03-02)

- 四大观点解读:2013半年度存储技术发展(05-24)

- Crossbar新型RRAM芯片 邮票大小存储1TB数据(07-07)

- 新一代数位储存方案强化安全监控应用(03-27)

- 大型数据存储中心高智能容错双总线系统设计方案(02-25)

- 存储虚拟化五步规划剖析(03-01)