运放电路中的电源噪声如何降低?

噪声可以是随机信号或重复信号,内部或外部产生,电压或电流形式,窄带或宽带,高频或低频。噪声通常包括器件的固有噪声和外部噪声,固有噪声包括:热噪声、散弹噪声和低频噪声(1/f噪声)等,在这里我们不予讨论。外部的噪声通常指电源噪声、空间耦合干扰等,通常通过合理的设计可以避免或减小影响。降低外部噪声的影响对发挥低噪声运放的性能至关重要。

常见外部噪声源

电源纹波

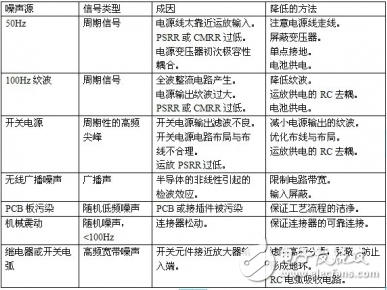

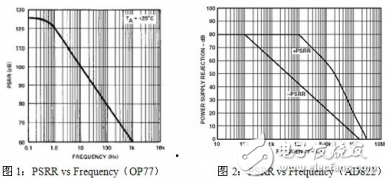

在全波整流的线性稳压供电的电路中,100Hz纹波是主要的电源噪声,对于运放电路,100Hz噪声电平通常要求控制在10nV-100nV(RTI)内,这取决于三个因素:运放在100Hz时的电源抑制比(PSRR),稳压器的纹波抑制比及稳压器的输入滤波电容的大小。图1是OP77的PSRR-频率曲线,可以看出,OP77在100Hz时PSRR大约是76dB,要获得不大于100nV(RTI)的性能,供电电源的纹波必须小于0.6mV。常用的三端稳压一般能提供大约60dB的纹波抑制能力,在这种情况下,稳压器的输入滤波电容必须足够大,以将输入端的纹波限制在0.6V以下。

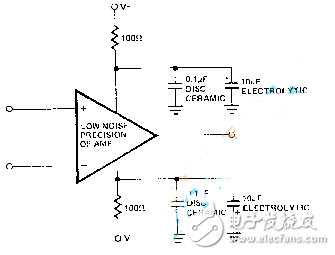

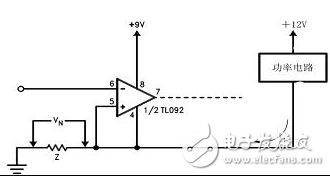

电源去耦

典型的串联稳压器供电的电源中包含有幅度为150uV,频率范围为100Hz-100KHz的噪声,开关型电源更严重,运放的PSRR在高频时以 20dB/Decade的速度降低,通过在电源脚加RC或LC去耦网络,能滤除大部分噪声,电路形式如图3。在使用RC去耦时,应该注意负载电流的变化会导致对电源脚上电压的调制。

图3:运放供电的RC去耦

电源调整率

任何电源电压的变化都会引起运放输入偏置电流的变化,图1中OP77的PSRR在DC时是126dB(0.5uV/V),电源电压的变化是一个潜在的低频噪声源。在低噪声运放的应用中,降低电源的纹波和提高电源的调整率都很重要,电源调整率不足通常会引起讨厌的低频噪声。

开关电源

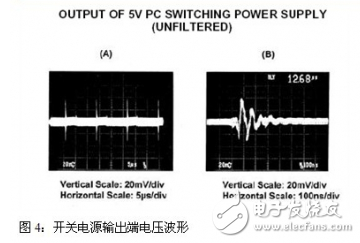

开关电源是一个很严重的噪声源,下图是典型的开关电源输出端的电压波形:

可以看出,噪声频谱既包含开关频率及其谐波成分,还包含开关回路谐振引起的阻尼振荡的高频成分,从几十KHz一直延续到几十MHz,而普通的运放在几百Hz以上时PSRR开始急剧下降,到几百KHz时几乎为零,此时,出现在输出端的电源噪声将很严重。

影响途径和对策

除了注意对运放PSRR或CMRR参数的选择和加强运放供电去耦(如采用RC去耦)外,在开关电源供电设计中,还应注意如下一些方面:

电源中的噪声可能通过基准源或PCB的漏电直接耦合到放大器的输入端。要注意对电压基准源输出的滤波,对于PCB漏电,可在信号输入引线与电源走线间加地线防护。

噪声可能通过PCB走线之间的分布电容直接耦合到放大器输入端,造成干扰。在PCB布线时,要注意电源线与弱信号线不要贴近平行走线,线净距大于线宽的3倍(3W原则),并在电源线或数字信号线与模拟小信号线之间加地线隔离。

接地处理不当,噪声通过公共阻抗影响敏感电路部分。为了防止公共阻抗将电源噪声引入信号回路,要注意如下几点:接地上避免带噪声的大电流流过前级小信号地;单点接地,电源、模拟、数字电路分开接地;布板使用地平面层,最小化地线阻抗;开关电源输出从最后一个滤波电容的地端引出电源地,避免从滤波电感前的电容的地端引出。

图5:共模阻抗噪声耦合示意图

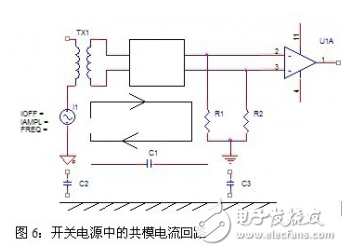

开关管漏极开关电压驱动的位移电流,通过初次级分布电容,次级电路,次级对大地与杂散电容,大地与初级地之间的杂散电容形成环路,次级模拟电路中流过的共模电流流过不平衡的阻抗转换成差模,对放大电路造成干扰(如图6)。共模方式引入的干扰一般为开关噪声中的高频分量(数MHz以上)。措施主要有如下三点:提供一条从开关电源次级地返回初级地的低阻抗噪声旁路通道,通常使用1000p~2200p的安规电容;使用共模扼流圈加强开关电源的输出的共模滤波;使用隔离技术,最小化回路中的共模电流。

通过空间磁场耦合到具有一定环路面积的信号回路或地线环中,造成对信号的影响。另外来自开关电源或市电网络的高频干扰可能通过空间杂散电容直接耦合到信号回路。设计中的考虑包括:合理的布局、调整电感线圈或变压器放置方向、优化布线,减小关键信号的回路面积,避免形成地环路可以减小干扰;双面或单面板布线,注意信号线和地线,电源线与地线一定要贴近平行走线;使用1000p电容射频多点接地,可以兼顾EMC和低频信噪比的需求;对敏感电路加屏蔽,注意屏蔽层连接到被保护信号的参考地;走线设计上注意电源线不要和信号线捆扎在一起。

小结

在运放电路设计中降低电源噪声的主要措施包括:

通过去耦、滤波等措施降低电源输出的纹波和

- 教你用示波器频域方法分析电源噪声(02-19)

- 示波器频域方法分析电源噪声(07-06)

- 传感器设计需要注意的四个问题(10-17)

- EMI噪声分析及EMI滤波器的设计(10-07)

- 开关电源的EMC设计(09-15)

- 多层线路板在开关电源电路中应用(11-07)