细说模拟信号采样与AD转换

满足Nyquist的采样定理?是,OK,否则增加点数N,重新计算2。

我们希望df越小越好,但实际上,df越小,N越大,计算量和存储量随之增大。一般取N为为2的整数次幂,不足则在尾端补0。

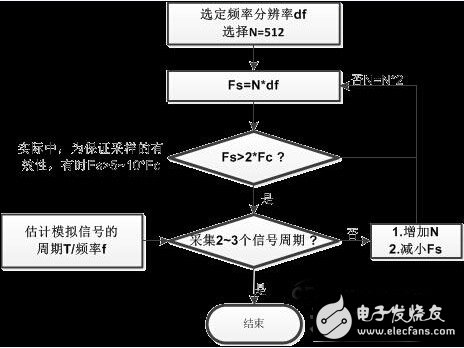

这里给出我的一个选择Fs的方案流程图,仅供参考。

采样后还有一个重要的操作是采样保持(S/H)操作,采样脉冲采样后无法立刻量化,这个过程要等待很短的一个时间,硬件上一般0.几个us,等待量化器的量化。

注意,在量化之前,所有的信号都是模拟信号,模拟信号就有很多干扰的问题需要考虑,这里只是从总体上给出我对整个过程的理解。更多细化的方案还需要根据实际信号进行研究。

量化

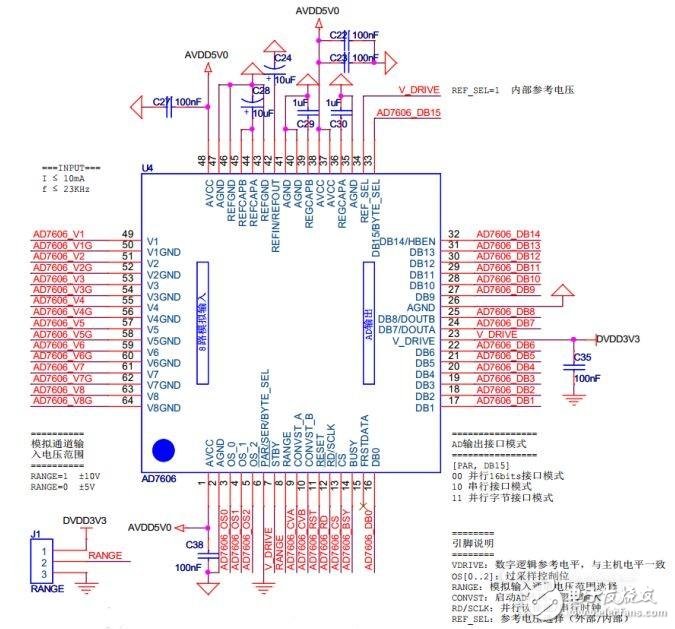

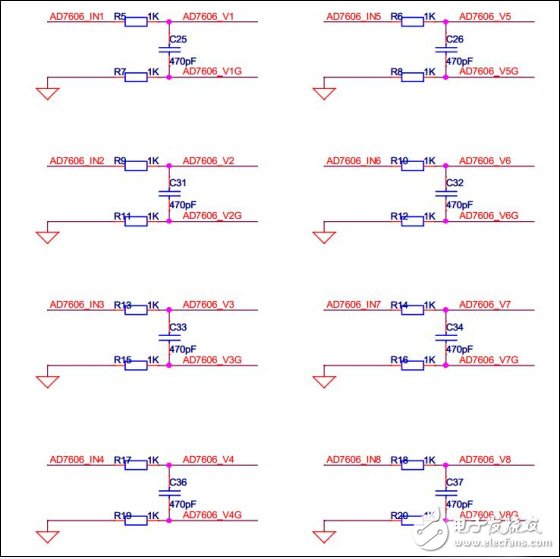

量化有个关键的参数,叫量化位数,在所有的AD转换芯片(如AD7606)上都能看到这个关键的参数,常见的有8bit,10bit,12bits,16bit和24bit。

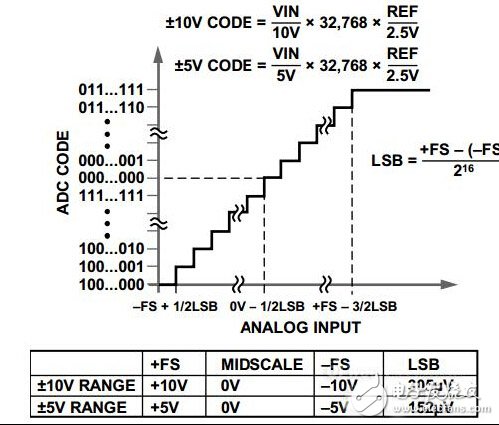

如上图,以AD7606为例,AD7606是16bit的AD芯片,量化位数指用16bit来表示连续信号的幅值。因此,考虑AD的测量范围(AD7606有两种:±5V和±10V),则AD分辨率是

±5V: (5V-(-5V)) / (2^16) = 152 uV

±10V: (10V-(-10V)) / (2^16) = 305 uV

量化位数越高,AD分辨率越高,习惯上,AD分辨率用常用LSB标示。

因此,AD7606中对于某个输入模拟电压值,因为存在正负电压,若以0V为中间电压值,范围为±5V时AD转换电压可计算为

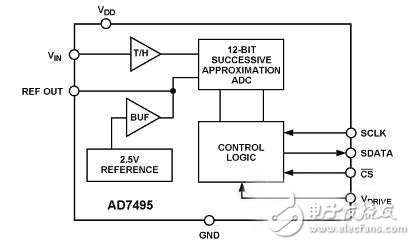

AD7606若使用内部参考电压,Vref=2.5V。哦对了,这又出现个参考电压。参考电压与AD量化的实现方式有关,从速度上分串行和并行,串行包括逐次逼近型,并行方式包括并行比较式,如下图(左:串行,右:并行)。AD7606是使用逐次逼近型的方式。

AD转换芯片另外两个重要参数是转换时间(转换速率)。并行AD的转换速率比串行的要高。但并行比较的方式中电阻的精度对量化有影响。

接着,我们还将介绍一个重要的概念:量化噪声。量化噪声对应量化信噪比,

SNRq = (6.02N + 4.77) dB

其中N为量化位数,且不去管这个公式是怎么得到的(详细推导可参考文献[2]),对于

N=12, SNRq ≈ 70dB

N=16, SNRq ≈ 94dB

从中可以看出:每增加1bit量化位数,SNRq将提高6.02dB,在设计过程中,如果对方有信噪比的要求,则在ADC选型时就要选择合适位数的ADC芯片。

明显的,并不是量化位数越高越好,量化位数的提高将对成本、转换速度、存储空间与数据吞吐量等众多方面提出更高的要求。同时,我们尽量提高量化噪声的前提是信号的SNR已经比较低了,如果信号的SNR比量化噪声还高,努力提高量化噪声将是舍本求末的做法。

- 经典案例分享:弱信号的测试(06-02)

- 虚拟远端采样控制器惠及视频安保(10-26)

- PWM控制的特点与方法(02-28)

- 以超低电感器 DCR 采样的电流模式开关电源(03-11)

- 分享来自凌特大牛关于LTC6804相关问题解决方案(06-20)

- 一种用AD7858提高DSP采样精度的新方法(05-01)